在本系列推文中,我們在上篇梳理了 FA 的起源、演變及其在半導體行業中的獨特地位,提出了指引 FA 工作的"第一性原理"與"兩大核心定理",旨在構建一個堅實的理論框架。今天,作為系列的下篇,我將結合兩個 FA 案例,具體闡述這些理論如何在實際工作中指導我們,從最初的失效信號出發,逐步定位、分析,最終找到問題根源並推動解決方案的形成。希望通過這些案例,能更直觀地展現失效分析工作的路徑與價值。

FA 的標準作戰流程(Workflow)

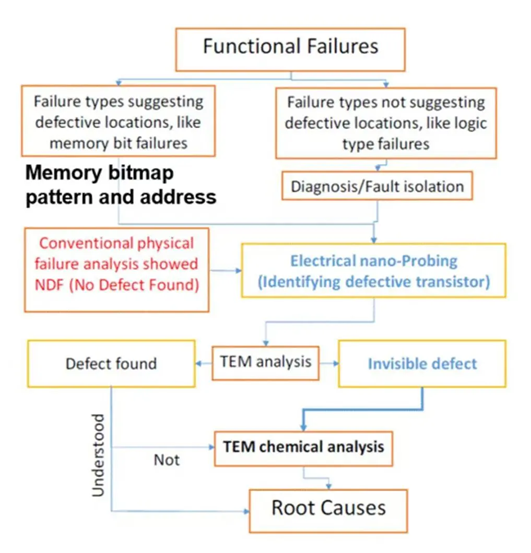

標準的 FA 工作始於一個清晰、嚴謹的流程。下圖(圖 1)展示了一個典型的 FA 流程範例,它源於一篇發表於 ISTFA 2015 的文章。在實踐中,每個 FA 單位的工程師團隊都會根據自身需求,設計出定制化的分析流程,並交付給資深的技術員團隊執行。FA 工程師的核心職責,是解決流程中遇到的技術瓶頸,並在現有技術不足時,提出創新的執行方案。此流程展示了從功能失效出發,經過失效確認與電性定位,再通過納米探針進行器件級的電性分析,繼而實施精密的物性分析(TEM/EDS),最終落腳于對制程根本原因的探索與討論。這是 FA 工作的一個完整閉環。

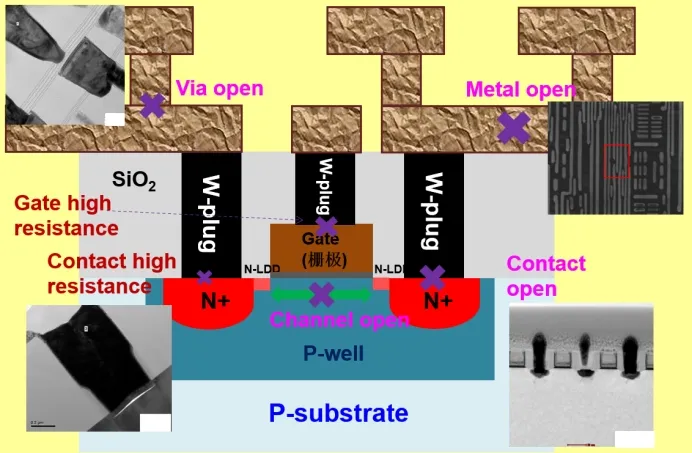

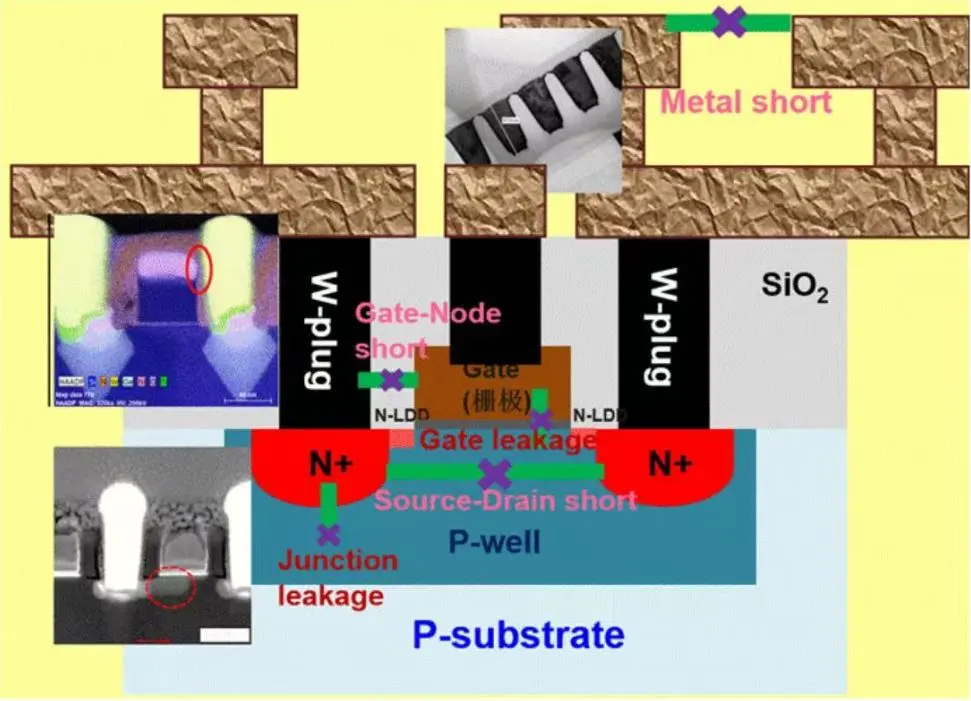

最常見的電路故障:斷路與短路

在半導體制程工藝中,我們遇到的問題,其電性異常的表現基本可歸為兩大類:高阻(斷路) 與 短路(漏電)。下圖(圖 2、圖 3)直觀地展示了可能導致這兩種失效的致命缺陷形態。為了更深入地說明理論如何指導實踐,以下我將分享兩個已發表的 FA 案例,作為後續討論的參考(為便於行文,將以第一視角陳述。)

案例分享(一):40nm RF芯片的"偽裝者 "——二級效應熱點

本文發表於 IPFA 2013:我們面臨一個棘手的良率問題——某 40nm RF 產品上出現了直流(DC)失效。

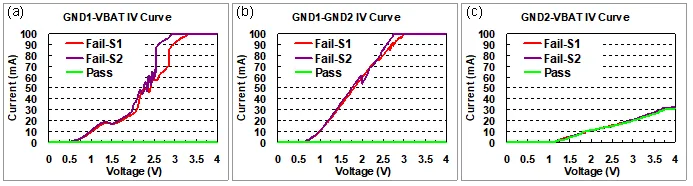

步驟 1:電性特徵分析 (EFA):針對可疑的 Pad 進行 I-V 直流測試,以判斷失效來源。測試結果(圖 4)非常明確:GND1 與 VBAT、GND2 之間均存在明顯的漏電路徑,而 GND2 與 VBAT 之間則表現正常。由 (a) 和 (b) 中的 I-V 關係可見,GND1-VBAT 與 GND1-GND2 是明確的漏電路徑。

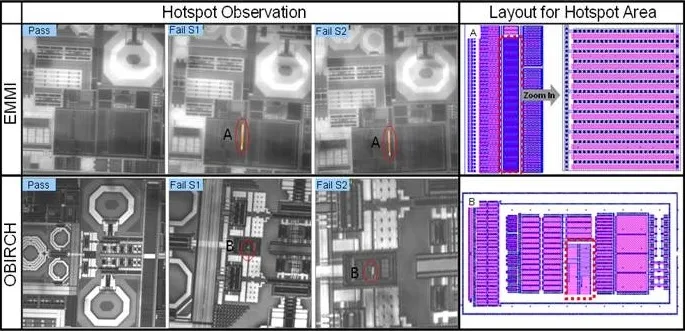

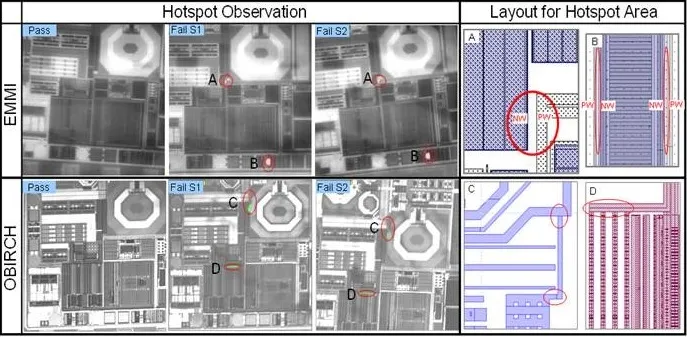

步驟 2:熱點定位。針對這兩條漏電路徑,我們隨即採用了熱點分析(EMMI/OBIRCH)進行定位。如圖 5 和圖 6 所示,在多個區域觀察到了異常的發光或發熱信號。在 PMOS 區域觀察到 EMMI 亮點,在 Resistor 區域觀察到 OBIRCH 熱點(圖5),在 N/P Well(二極管)區域觀察到 EMMI 亮點,在 Resistor 區域觀察到 OBIRCH 熱點(圖6)。

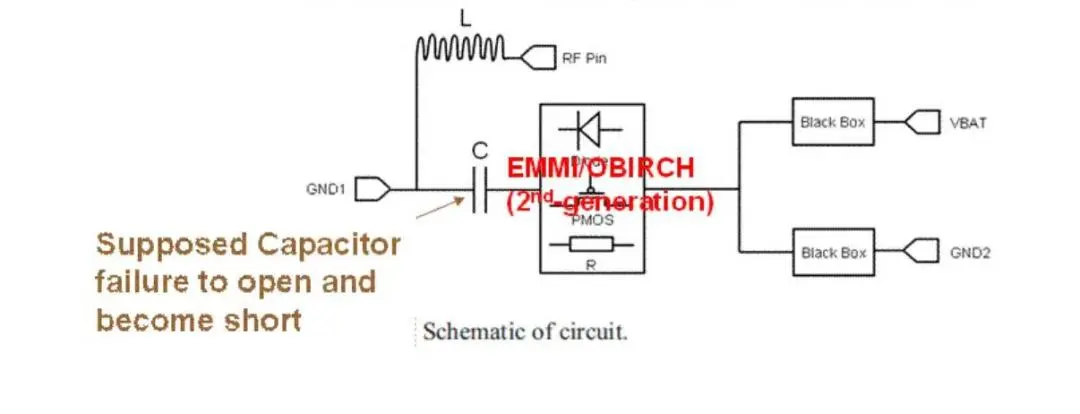

步驟 3:線路分析與關鍵推論。此時,案件似乎變得複雜。但經過深入的線路分析(Circuit Analysis),我們提出了一個關鍵推論(圖 7):真正的失效點可能位於一個電容器上,而非我們觀察到熱點的 PMOS、Diode 或 Resistor 等處。我們推斷,電容 C 的非正常漏電是根因。我們觀察到的亮點,實際上是漏電電流流經 PMOS 等器件時產生的 " 二級效應熱點 "(2nd generation hot spot),它們只是電流路徑上的 " 症狀 ",而非 " 病灶 "。

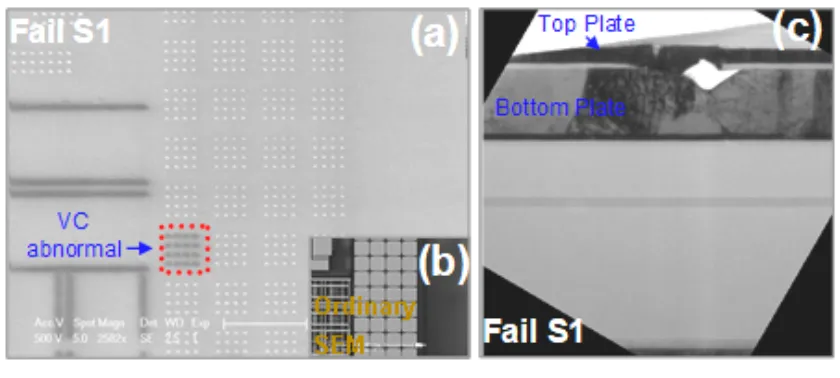

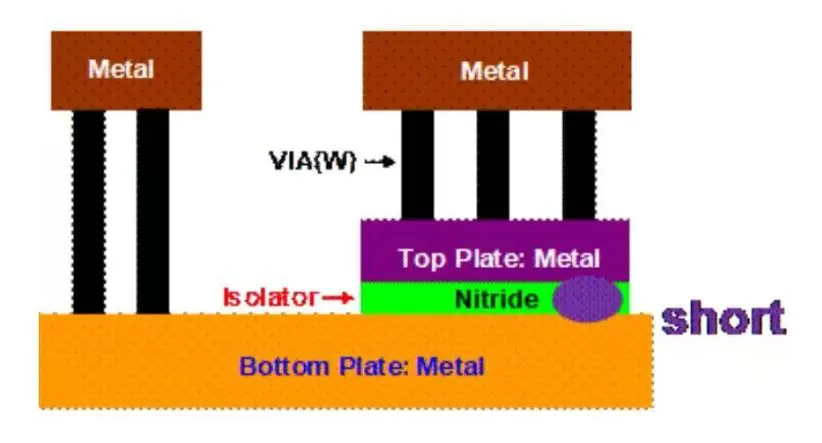

步驟 4:PFA 驗證。為了找到物理證據,我們進入 PFA 階段。首先,通過低加速電壓的 SEM VC 技術,我們成功在可疑位置觀察到了漏電信號(圖 8a)。隨後,最終的 TEM 截面分析(圖 8c)一錘定音:電容器的上下極板確實發生了短路,中間的介電層已被完全破壞。(a) Low-kV VC 成功定位漏電位置;(b) High-kV VC 無信號;(c) TEM 圖像清晰顯示電容器介電層被擊穿,導致短路。圖9與圖 8(c) 的 TEM 截面圖相對應,清晰展示了金屬層與電容的結構關係。

結論與改善:線路分析顯示,失效點附近存在電容與電感並存的結構。這類 LC 結構在制程中如同 " 天線 ",會收集大量電荷,最終導致電壓擊穿電容的介電層。基於此結論,最終的改進措施由設計端提出:將電容 C 與電感 L 的位置分開,從而避免了電荷的過度累積,根除了此類器件損壞。

案例分享(二):28 nm 芯片的 " 隱形 " 漏電 ——動態測試的關鍵性

本文發表於 IPFA 2016,背景: 我們發現一款 28nm 移動應用 IC 遭遇了 high sleep IDDQ 問題,漏電值從 200µA 的標準放大至不可接受的 >2mA。

步驟 1:初步 EFA 的挑戰。按照正常流程,我們首先進行靜態 I-V 測試與熱點觀察,結果卻一無所獲。我們很快意識到,這是因為簡單的直流偏壓無法使芯片的電源管理功能進入特定的 "sleep mode",也就無法複現失效。這也正是 IDDQ 測試的特性。

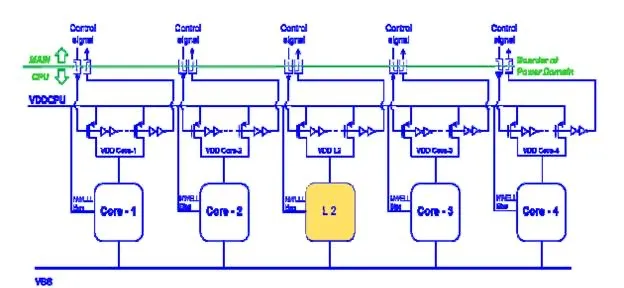

步驟 2:動態測試與定位。此案凸顯了我在定理二中強調的 "失效分析必須與測試緊密相連 "。我們引入了測試機,成功地將芯片置於 sIDDQ 模式,並捕捉到了真實的漏電量。在此狀態下,我們成功定位到熱點(位於 L2 層,具體圖片因保密未展示)。

步驟 3:診斷與排查。根據線路圖,我們推斷問題可能出在MTCMOS或SRAM區域。我們的調查隨即成為一個排除過程:(1)診斷 MTCMOS:利用 FIB 進行電路編輯,強行關閉 MTCMOS 的電源使其進入 Off-state。再次測量 sIDDQ,發現漏電量並未減少。(2)鎖定 SRAM:排除了 MTCMOS 後,嫌疑便聚焦於 SRAM 區域。

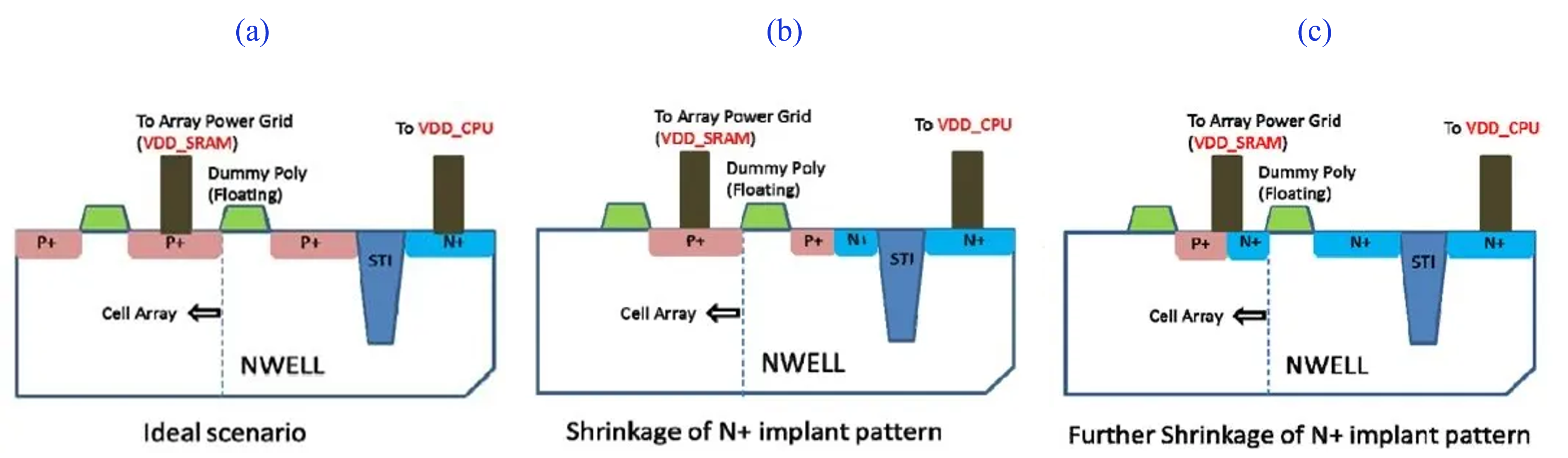

步驟 4:建立失效模型與先進表徵。我們提出了一個可能的失效模型(圖 11):在離子注入工藝時,光刻膠的覆蓋不完整,導致本應注入 N-well 的 N+ 離子," 侵入 " 了鄰近的 P+ 區域,從而在 Vdd 與 GND 之間形成了一條非預期的漏電通路。

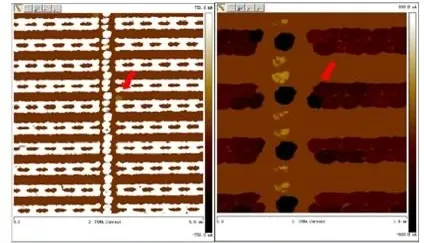

這種摻雜級別的異常,是傳統電鏡分析(如 SEM VC)的盲區。因此,我們採用了一種更先進的表徵手段——導電原子力顯微鏡(C-AFM)。如圖 12 所示,C-AFM 成功地在 PMOS 的 Contact 上偵測到了異常的漏電信號,這為我們的失效模型提供了強有力的間接證據。在正偏壓下(左圖),本不應導電的 PMOS CT 上出現了清晰的漏電信號,證實了我們懷疑的失效模型。

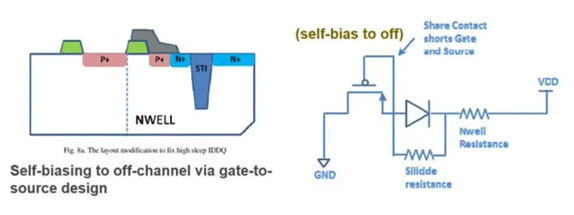

結論與改善:基於分析結果,我們採取了兩種方案來解決問題:(1)工藝端:利用 OPC 來優化光刻圖形,確保光刻膠輪廓的正確性,避免 N+ 注入異常(成本較高)。(2)設計端:重新設計成一種 " 自關閉 " 線路(圖 13),這種設計即使在發生輕微注入異常時,也能通過 Gate-to-Source 短路來自動關閉 PMOS 溝道,從而規避漏電。這是一種非常巧妙的設計,尤其適用於在 Array 邊緣等工藝弱點區,能有效防止意外漏電。兩種方案的成功,最終確認了 N+ 注入缺陷是此次漏電的根源。

以上兩個案例,旨在說明一個完整的低良率 FA 案件的分析思路。無論是處理可靠性測試後的問題,還是客戶退貨的澄清,其核心的工作思路與分析流程都是觸類旁通的。

作者介紹:賴李龍 博士

出生於臺灣,清華大學(台)物理學士、碩士,復旦大學材料科學博士。從事半導體製造行業從業超過27年, 在台工作期間曾任職功率器件與DRAM廠, 在中國大陸服務期間經歷過中芯國際、芯恩、華為等半導體製造大廠, 制程工藝參與從250nm成熟制程量產到5nm的先進技術的研發與良率提升等工作。工作服務期間發表了25篇國際會議技術文章與期刊文獻, 同時申請15份以上的專利。歷練過專業晶圓代工/DRAM存儲器/功率器件/新型非易失性存儲器(FRAM)/IDM等集成電路製造多元性工廠為主的半導體公司。對於半導體物理與器件,物性顯微表徵與電性失效分析均有較高的實務經驗與深入的學理基礎。