第一階段 —— 創業期(Start-up)

台積電成立於 1986 年,董事長為 張忠謀(Morris Chang),他此前剛從美國返台,出任 工業技術研究院(ITRI) 院長。創立初期的資金為 4,800 萬美元,來源包括:台灣 行政院開發基金(48.3%),荷蘭飛利浦(Philips)(27.5%),其餘來自其他台灣企業(在政府「協調」下投資)。1988 年又進行了兩輪募資,分別為 2,900 萬美元與 2.05 億美元,總資金達 2.82 億美元。1987 年開始量產,最初是在租用的 ITRI 6 吋晶圓廠中,使用來自 ITRI 的 2 µm 與 3.5 µm 製程技術。隨後很快為 Philips 客製化推出 3.0 µm 製程,這大概是台積電第一個真正具備量產規模的製程。

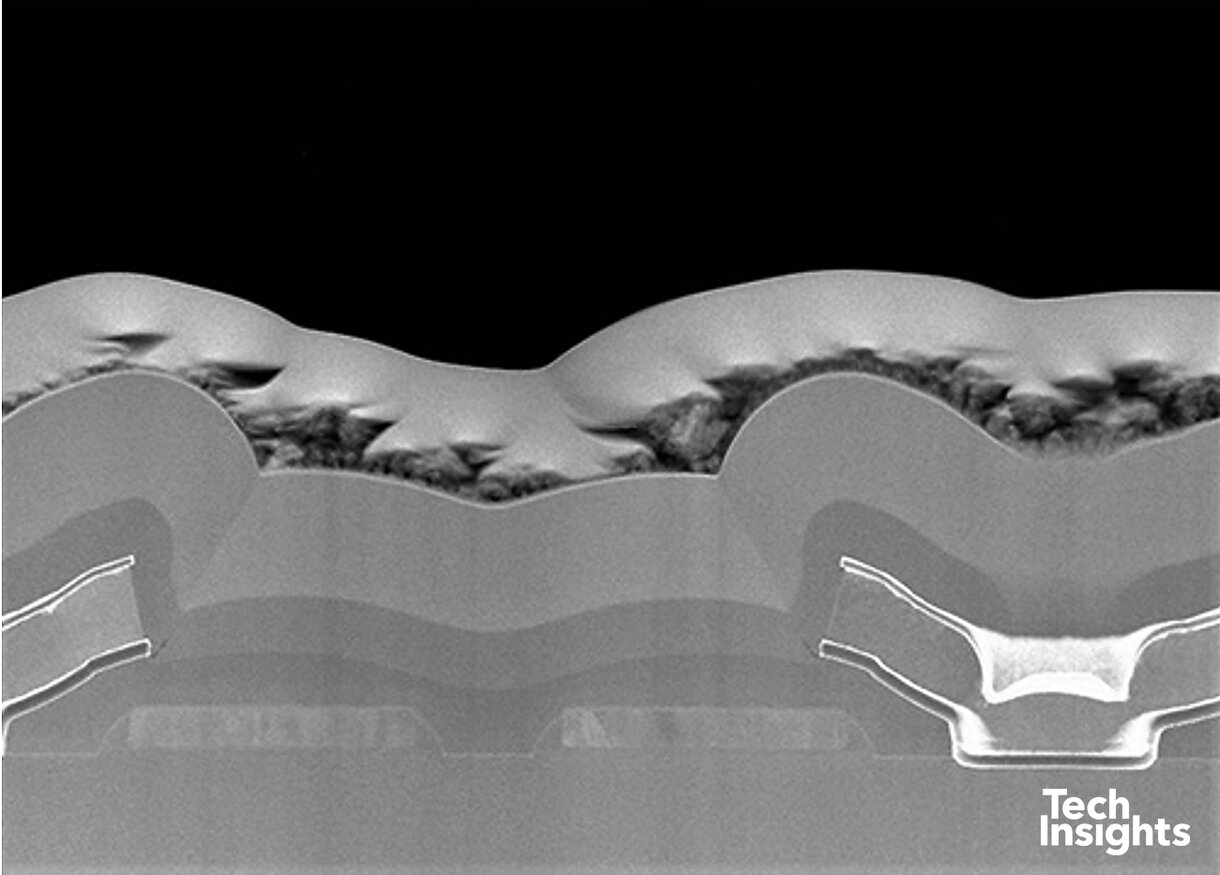

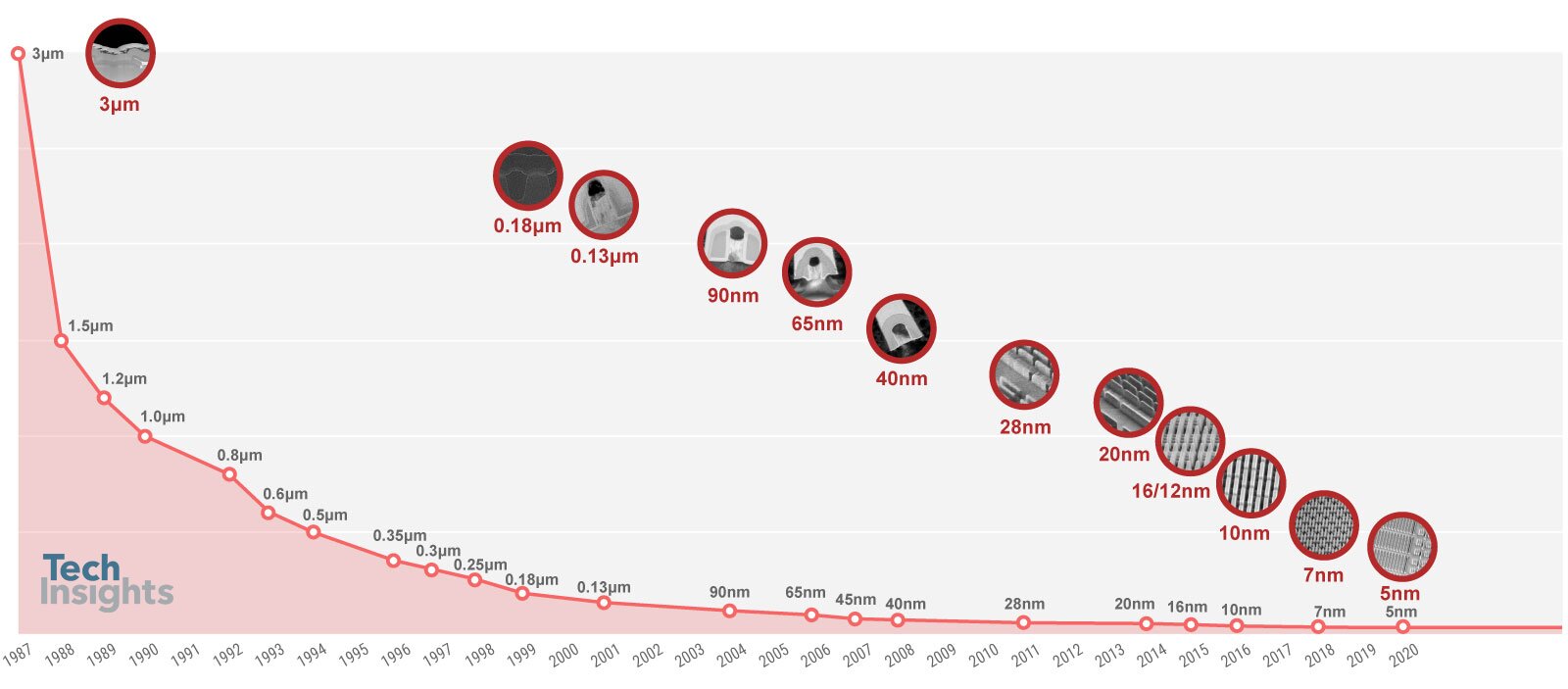

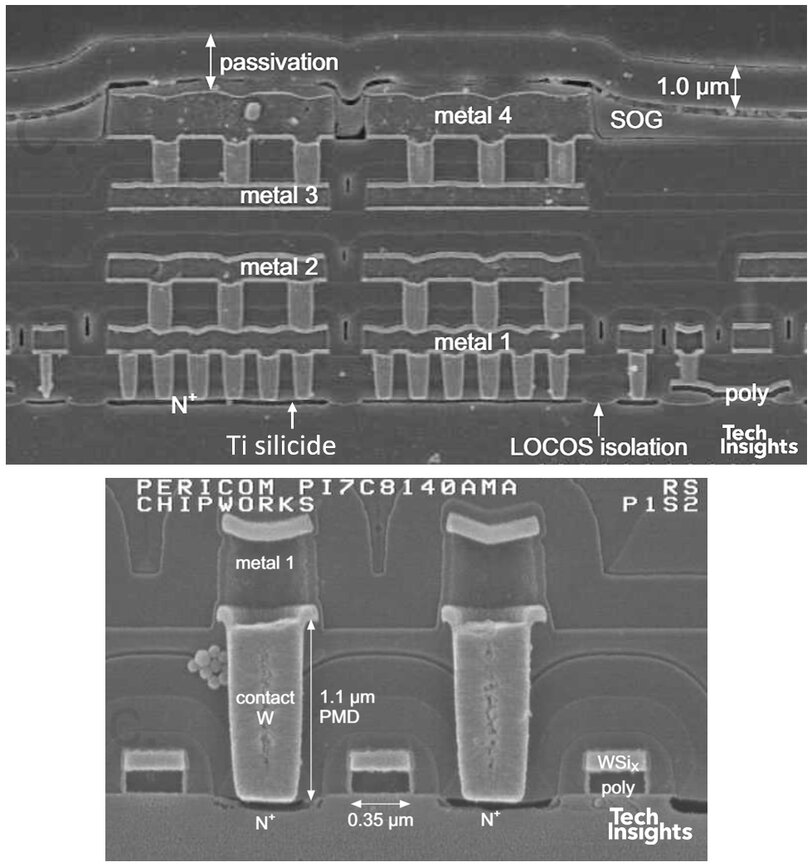

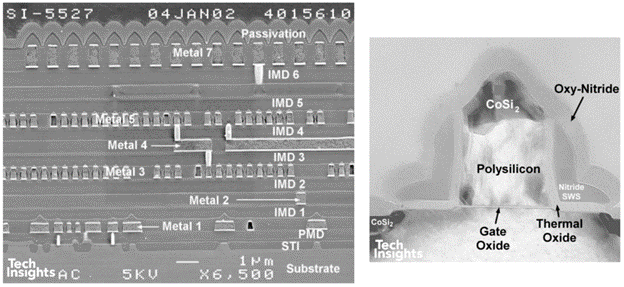

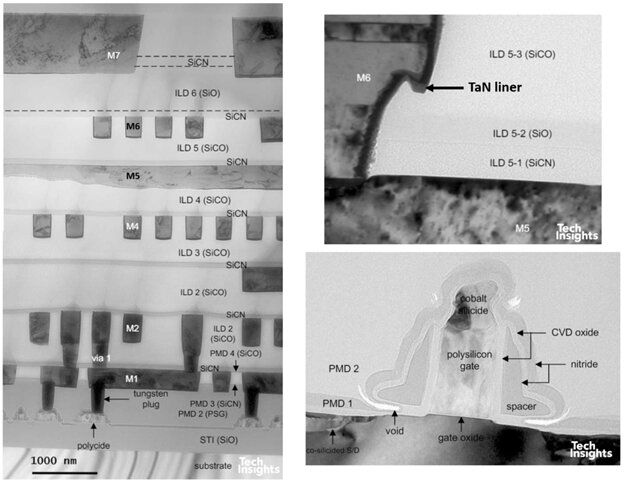

如圖所示,這是一種 單多晶矽(single poly)/單金屬(single metal) 製程;我們特別標註了結構,因為大概得 60 歲以上的人才會對這種技術有直覺印象!接著在 1988 年,台積電迅速推出 1.5 µm 製程。製程節點的快速演進,在其官網所展示的這張圖中表現得相當清楚:

上市與 0.6 µm 時代,1994 年,台積電正式上市。當時已發展至:0.6 µm、三層金屬(3-metal)邏輯製程;雙多晶矽、雙金屬(2-poly / 2-metal)的混合訊號製程;1.0 µm BiCMOS 製程。同時已有 Fab IIA 與 Fab IIB 投產,並開始建置 8 吋晶圓的 Fab III。在 1990–1994 年間,台積電出貨 250 萬片晶圓,營收由 新台幣 22 億元 成長至 193 億元,晶圓代工模式已明顯起飛。

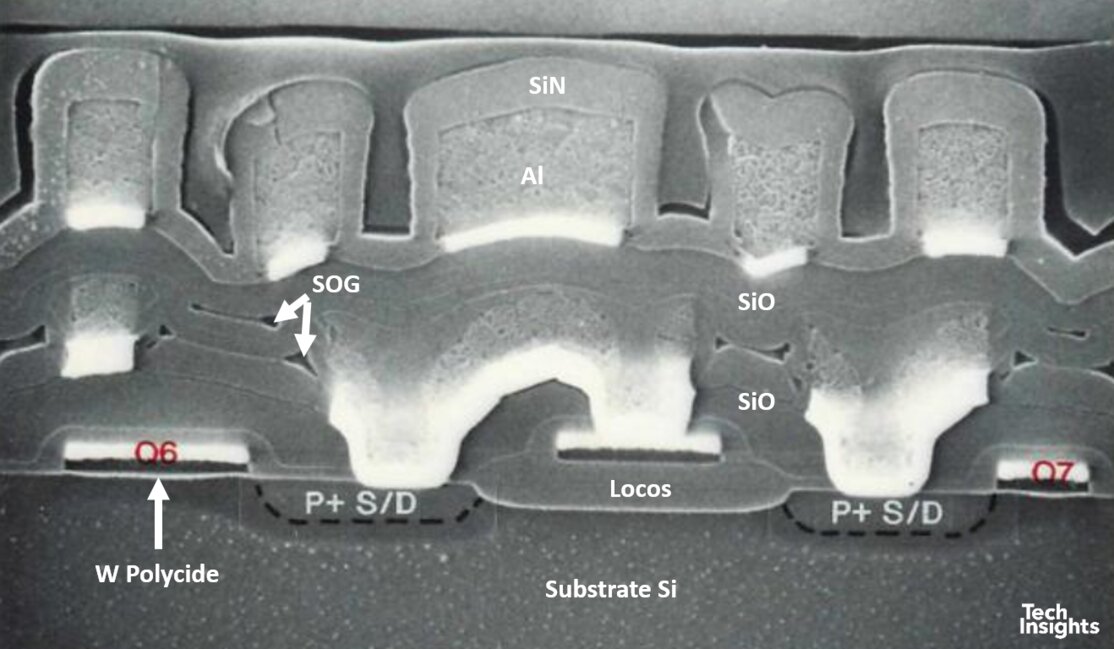

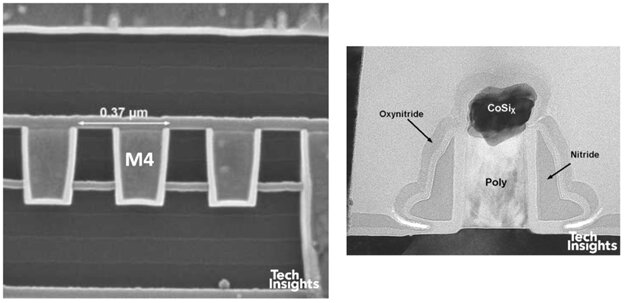

上述 Altera 的 EPLD 只使用 雙金屬層的 0.6 µm 製程。我們可以看到,當時的平坦化(planarization)主要依靠:流動玻璃(PSG / BPSG),旋塗玻璃(SOG),氧化層沉積與 etch-back。這種方法在 三層金屬以下尚可接受,但金屬層數再增加,表面起伏就過於嚴重,鋁金屬的步階覆蓋能力已無法承受。ICE 的評估指出:接觸孔內的金屬厚度可能被削薄達 75%。ICE(Integrated Circuit Engineering) 是一家位於鳳凰城的公司,2001 年被 Chipworks 併購,其報告目前仍可在 TechInsights 查閱。我們為了找這些資料,確實翻找了很久。此時 閘極已導入鎢矽化物(WSi),但 源/汲極尚未使用;而 LOCOS 仍是主要的元件隔離方式。

第二階段 —— 擴張與追趕(Expansion and Catch-up)

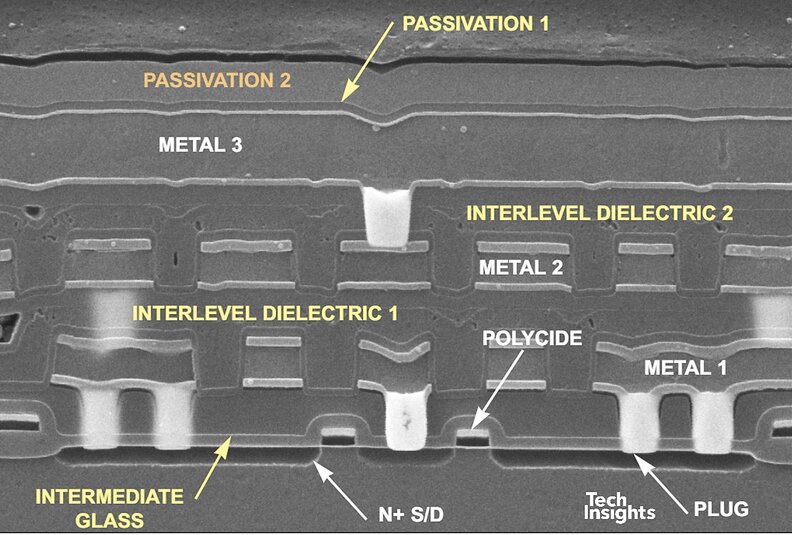

1995 年,8 吋 Fab III 啟用,並導入 鎢插塞(tungsten plugs)。插塞仍採用沉積加 etch-back 的方式製作,儘管 IBM 早已開發 CMP(化學機械研磨)。即便如此,插塞的引入仍改善了平坦化程度,使得更多金屬層成為可能。

到了 0.35 µm(1997 年),台積電正式採用 CMP,並在 源/汲極使用鈦矽化物(Ti silicide),但閘極仍為鎢矽化物。

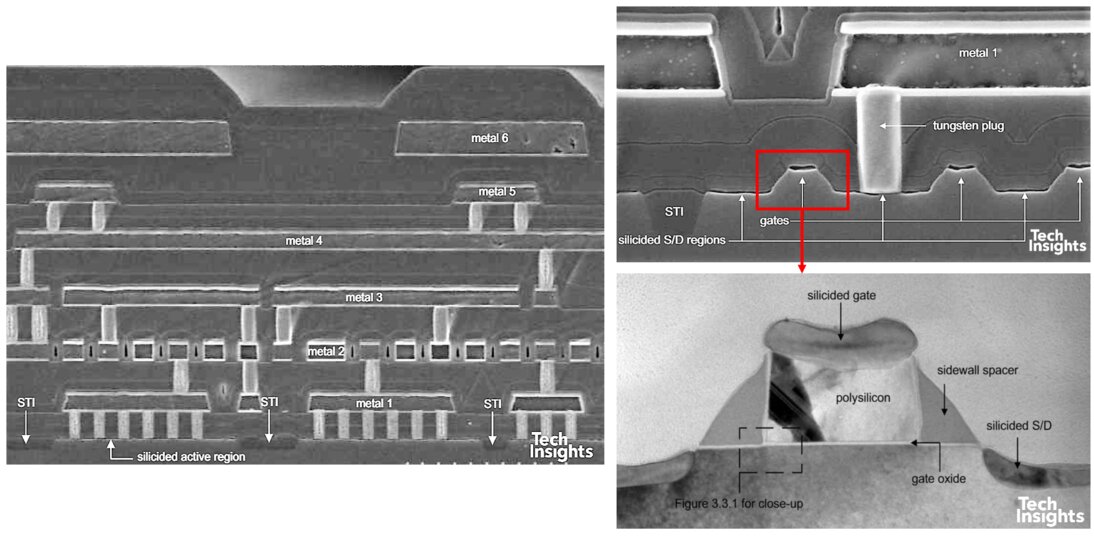

同樣在 1997 年,台積電開始了「半節點(half-node)」的慣例,推出 0.3 µm 製程,並啟用 Fab V。隔年,我們看到了首批 0.25 µm 產品:完整 CMP 製程,六層金屬,完全自對準 Ti silicide(Ti salicide),首次導入淺溝槽隔離(STI)。

在商業面,1998 年台積電營收達 新台幣 500 億元,即便當年是半導體產業的景氣衰退年,仍出貨 120 萬片 8 吋等效晶圓;同時,美國 俄勒岡州 Wafertech 廠也開始出貨。近期,台積電前研發副總 蔣尚義 在電腦歷史博物館的口述歷史中提到:0.25 µm 製程曾使用氟矽玻璃(FSG)作為低 k 介電層,但我們的分析報告中並未發現相關證據。他也指出該節點的開發極為困難,但仍如期完成。

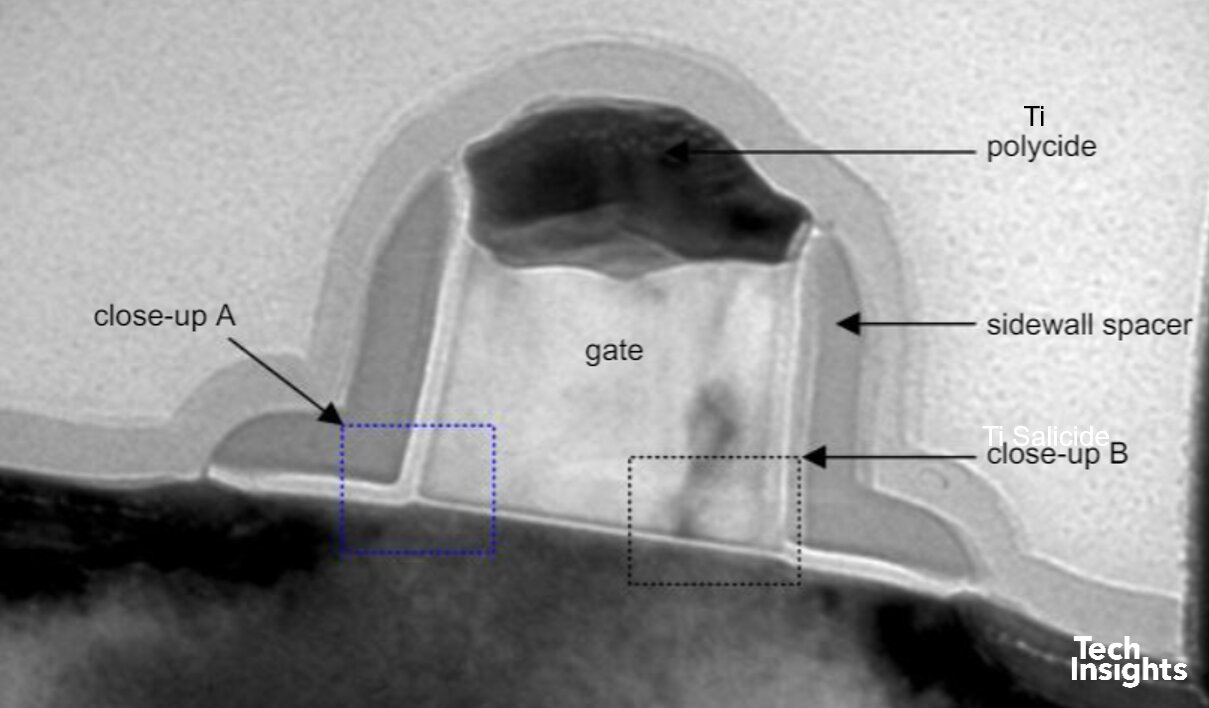

0.22 µm 與 0.18 µm:1998 年也開始量產 0.22 µm 製程,外觀與 0.25 µm 類似,但電晶體結構有所改變:仍使用 Ti salicide,但側牆間隔層(spacer)改為 L 形,不再是三角形。閘極長度已縮短至 0.16 µm,此時「節點名稱」與實際尺寸開始失去直接對應關係——在 0.25 µm 之前,閘長仍是相當可靠的世代指標。

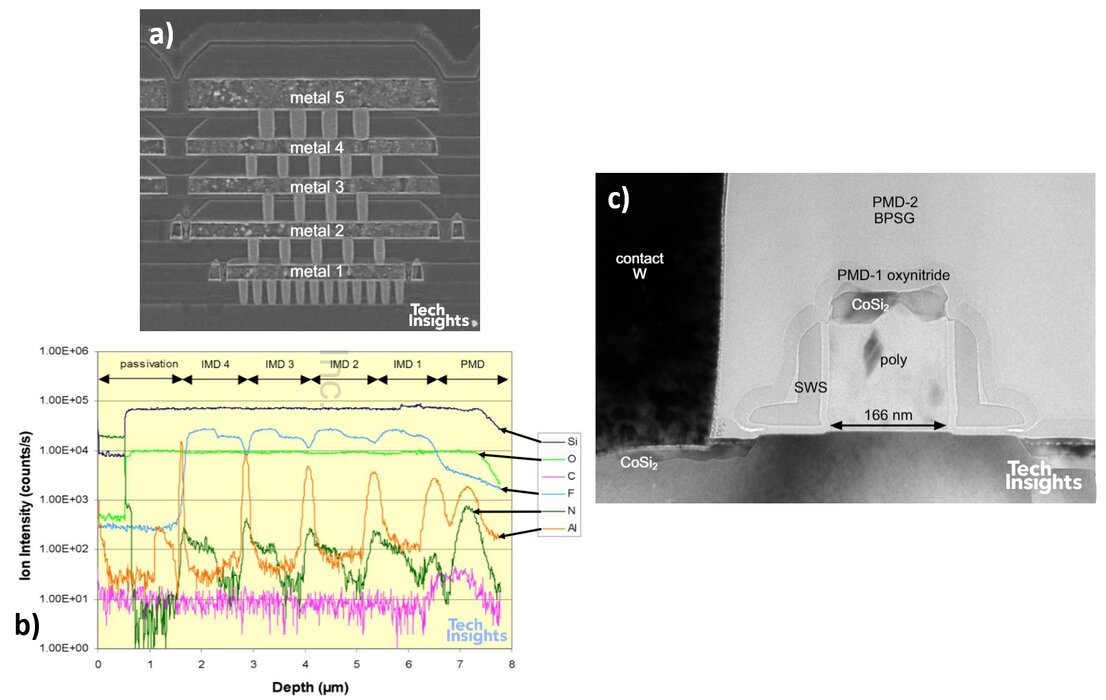

到了 0.18 µm(180 nm,2000 年):後段製程明顯改變,介電層堆疊中確認使用 FSG(k ≈ 3.6,相較於 SiO₂ 的 ≈ 4.0),Fab VI 啟用,並內建 300 mm 試產線。電晶體仍為 L 形 spacer,但矽化物改為 鈷矽化物(Co salicide),閘極長度約 130 nm。該 Lucent 晶片具有 五層金屬,我們也分析過 七層金屬的版本。

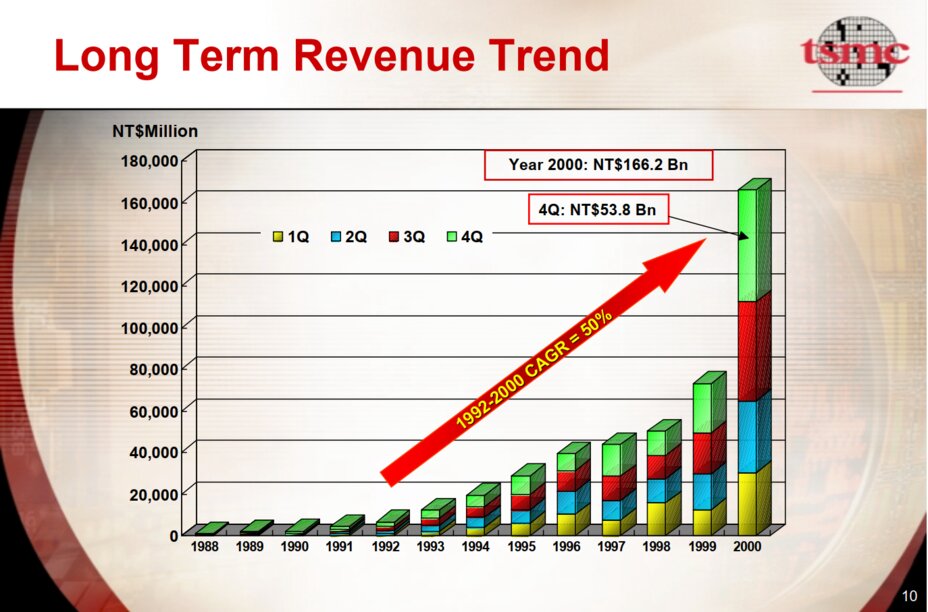

千禧年的高峰,2000 年是台積電的爆發年:營收較 1999 年成長 127%;1992–2000 年年複合成長率高達 50%。同年也推出了 150 nm 世代,延續半節點策略。在研發端,**130 nm(銅製程)**與 300 mm 晶圓製程同步進行,而 新竹 Fab 12 與 台南 Fab 14 也正施工中。

第三階段 —— 與同業並駕齊驅,甚至短暫領先

到 1998 年,也就是 0.25 µm 製程正式推出的時點。台積電前研發副總 蔣尚義 在其口述歷史中提到:當他於 1997 年加入台積電時,台積電的技術論文仍無法被 IEDM 或 VLSI Symposium 等頂級國際會議接受。然而,到了 1996 年,晶圓代工模式已獲得學界與產業界的認可,當年台積電營運資深副總 曾繁城(F.C. Tseng) 便在 IEDM 發表了大會主題演講(plenary talk)[1]。我們也在 VLSI 1998 的論文中找到了台積電 0.25 µm 技術的詳細介紹 [2]。0.18 µm(180 nm)製程則是在 VLSI 1999 發表 [3],有趣的是,該論文提到使用 旋塗式低介電常數材料(spin-on low-k dielectric)——氫倍半矽氧烷(HSQ, hydrogen silsesquioxane)——來進行平坦化。蔣尚義對此有一段親身經歷的回憶:我們測試後,結果非常好,所以就用 HSQ 取代 FSG(氟矽玻璃)。效果很好……在研發階段,我們做了可靠度認證,量產前也通過所有標準。但當進入大規模生產後,可靠度問題開始出現,而且是在已經量產之後的最後關頭才被發現。那時正好是聖誕節前後,我們立刻決定把 FSG 換回來,於是日以繼夜地趕工,沒有聖誕節、沒有新年、沒有農曆新年,在極大的壓力下,終於把問題解決。雖然晚了些,但結果是好的。」這是一個典型例子,說明 研發階段看似成功的技術,在進入量產時仍可能遭遇重大挫折。類似地,IBM 也曾在其 SiLK 旋塗式低 k 材料上遇到問題,最終回退至 CVD 製程。

可以說,從 180 nm 節點開始,台積電已與其他一線大廠站在同一水準上——在尺寸上可能略慢幾個月,但在 FSG 的導入上反而略為領先。IBM 與 Intel 也在 1998–1999 年推出 180 nm,但我們沒有發現其使用 FSG 的紀錄。此外,台積電也在 2000 年自 台南 Fab 6 的 12 吋試產線出貨 300 mm 客戶晶圓。150 nm 節點基本上是 180 nm 的微縮版,具有 七層金屬與 FSG 介電層。

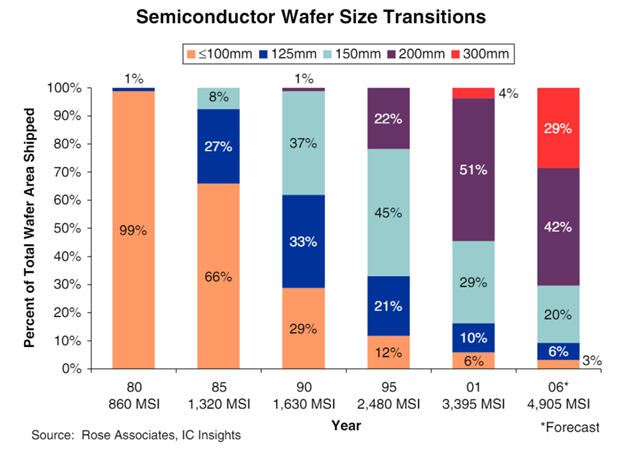

2001 年是 IC 產業史上最糟的一年,市場衰退達 32%。即便如此,150 nm 產品在第四季仍占 21% 的營收;Fab 12 也開始 300 mm 量產。令人意外的是,即使在景氣低迷期間,300 mm 晶圓在 2001 年仍占總出貨量的 4%。

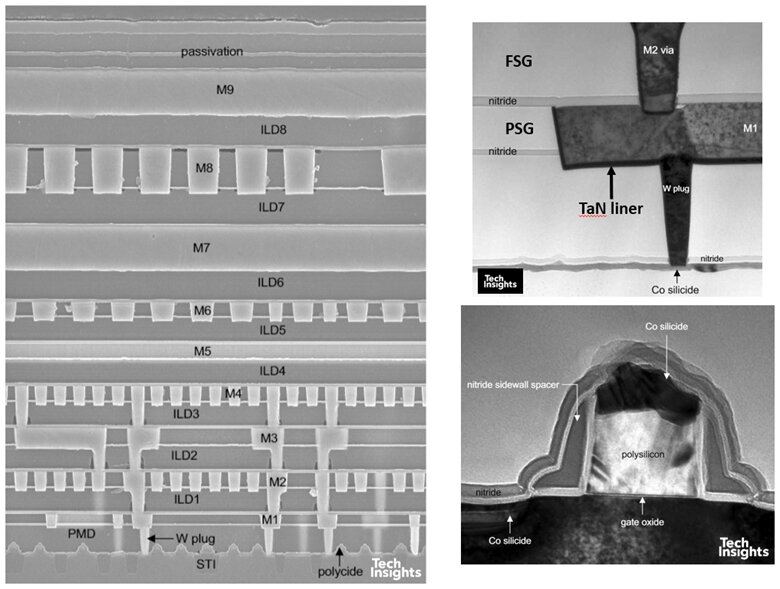

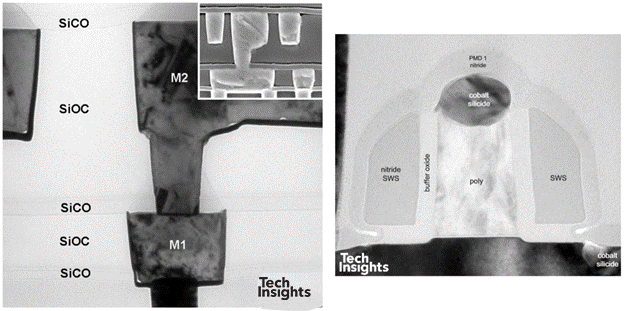

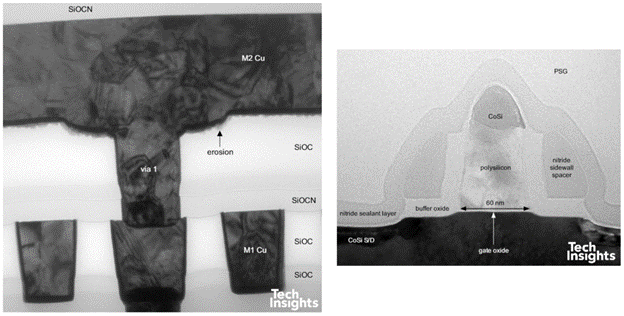

2002 年標誌著 ITRI Fab 1 的租約結束與退役,同時 130 nm 世代正式量產,並在第四季貢獻 8% 的營收。後段金屬/介電層堆疊中的 RC 延遲問題,持續推動 **銅金屬化(Cu metallization)**與 低 k 介電層的需求。IBM 已在 180 nm 導入銅製程,隨著尺寸持續微縮,其餘業界勢必跟進。在 150 nm 與 130 nm 節點,台積電初期導入 銅金屬 + FSG 介電層。其結構為:金屬一(M1):單鑲嵌(single damascene)銅,搭配 鎢插塞(W plug)(因銅若擴散至基板會嚴重影響載子生命期),其餘金屬層:雙鑲嵌(dual damascene)。

2003 年 4 月,台積電宣布 130 nm 真正低 k(true low-k)版本,採用 Applied Materials 的 Black Diamond 技術。所謂「真正低 k」,指 k ≤ 3.0;Black Diamond 標稱 k ≈ 2.8 [4]。起初兩者皆於 200 mm 晶圓生產;隨著銅製程成熟、300 mm 產線擴張,台積電成為 全球第一家大量出貨「銅 + 低 k」產品的公司,其中部分產品甚至已在 300 mm 晶圓上量產。回顧來看,這使台積電領先其他晶圓代工與 IDM(如 Intel、IBM)。我們看到的首批產品是一顆 ATI 繪圖晶片,時間約在 2003 年底。

如往常,台積電在 90 nm 之前推出 110 nm 半節點(約 130 nm 的 10% 縮小)。此 NVIDIA 範例顯示其可能同時進行了 成本最佳化,因為並未使用低 k(對 GPU 來說稍顯意外)。相對地,其溝槽與通孔蝕刻精度明顯優於 ATI 的 130 nm 版本。

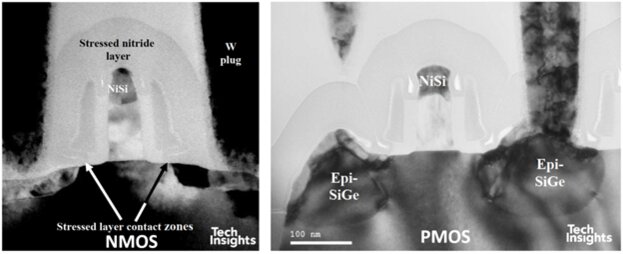

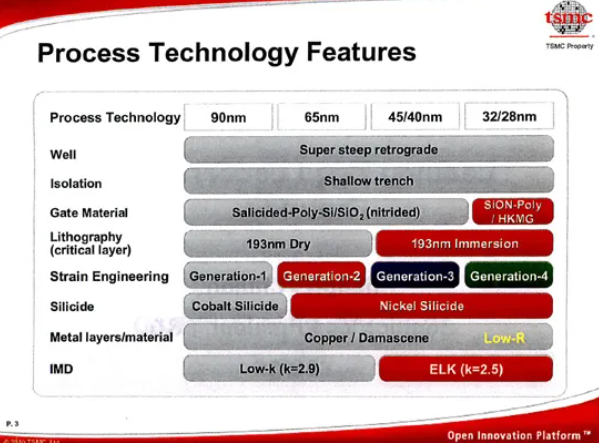

90 nm:奈米世代的正式登場。2004 年是 90 nm 的關鍵之年,產業正式由微米(µm)命名轉向奈米(nm)。這一年對 CMOS 也是分水嶺:Dennard Scaling(同時縮短閘極長度、氧化層厚度與操作電壓)達到極限,因為閘極氧化層已薄至 ~1.0–1.2 nm,載子開始穿隧,導致漏電與功耗急遽上升。Intel 在 130 nm 放慢腳步、低 k 與銅製程導入較晚,但在 90 nm 憑藉 應變矽(strained silicon) 重新取得技術領先,以提升載子遷移率。其他公司(IBM、AMD、Fujitsu)亦採用張應力氮化層;Fujitsu 與 TI 使用晶圓旋轉;唯有 Intel 使用嵌入式 SiGe S/D 來增強 PMOS。

第四階段 —— 300 mm、整併與主宰的開始

台積電 90 nm 製程是首個 完全以 300 mm 晶圓量產的節點,並宣稱為「全球第一個進入全面量產的 12 吋、低 k、90 nm 製程」,當年即被 超過 30 家客戶採用。Chipworks 分析的產品為 Altera Stratix-II FPGA,其特點為:10 層金屬(9 Cu + 1 Al);M1–M6 使用低 k;電晶體結構並非單純由 130 nm 縮小,而是修改了 側牆 spacer 結構,不再是典型的 L 形。與 Intel 相比,其氮化層似乎過薄,難以作為有效的應力層。另一項重要特色是:第二代低 k 製程,其溝槽與通孔蝕刻明顯更乾淨,帽層由 SiCN 改為 SiCO。

在上市十年後,TSMC 已擁有兩座 12 吋晶圓廠、五座 8 吋晶圓廠以及一座 6 吋晶圓廠,另外還有兩家全資子公司——美國的 WaferTech 與中國的台積電(上海)有限公司,以及一家位於新加坡的合資晶圓廠 SSMC。TSMC 及其關係企業的年裝置產能合計為 480 萬片 8 吋等效晶圓。在此期間,公司的中央研發(Corporate R&D)持續投入於新型電晶體與製程技術的研究,例如 SOI、FinFET、MRAM、高-k 閘極介電層、金屬閘極、應變矽(strained-Si),甚至奈米線(nanowires)。其中提到 FinFET 可能會令人感到意外,直到我們想起 胡正明(Chenming Hu)在 2001–2004 年間擔任 TSMC 的 CTO(而胡正明在 1999 年即發表了第一篇 FinFET 論文)。TSMC 也是最早與ASML以及Nikon合作研究浸沒式微影(immersion lithography)的公司之一,並於 2004 年接收第一套 ASML 系統;同年對外宣布 90 nm 測試晶片成功運作,並在 2006 年初於 12 吋晶圓上達到接近量產水準的缺陷密度 0.014/cm²

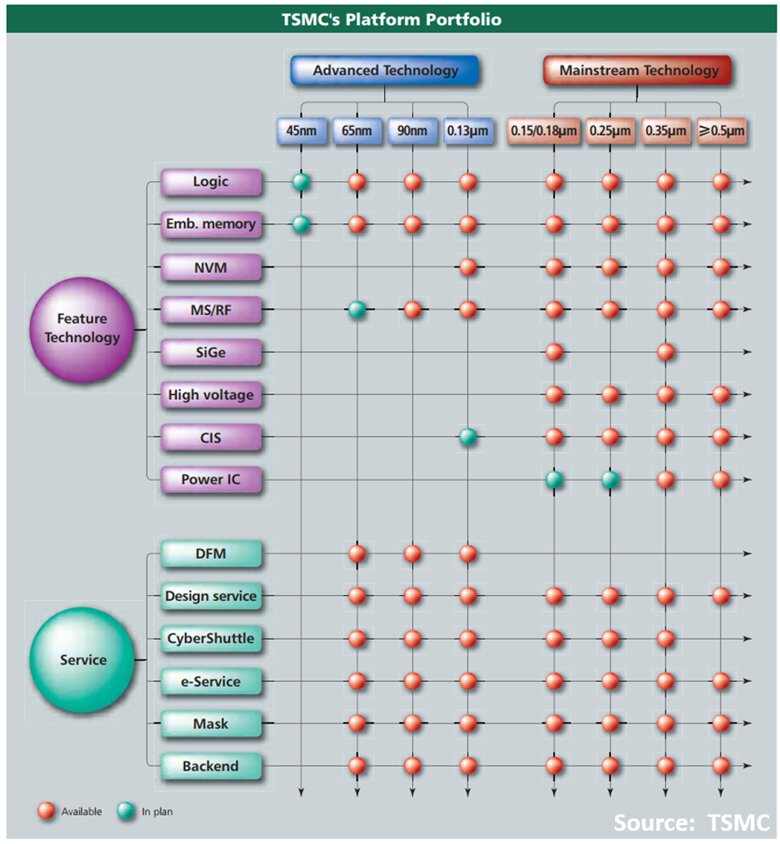

自創立初期起,TSMC 即在基礎邏輯製程之上提供多種變化版本,例如 **混合訊號、嵌入式記憶體、非揮發性記憶體以及高電壓製程;到了 2000 年代中期,這些產品被策略性地整合為兩大「平台」——先進技術(Advanced Technology)與主流技術(Mainstream Technology)。

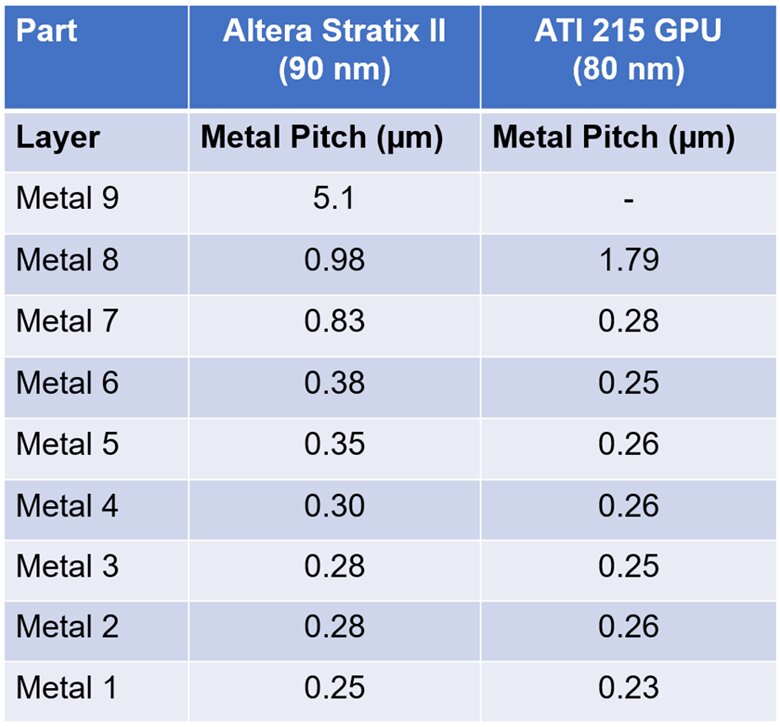

我們沒有時間與篇幅深入討論這些「主流」產品的細節,但值得注意的是,150 nm 及以上節點、以 6 吋與 8 吋晶圓生產的產品,在 2006 年仍占總銷售額的 50%。2006 年初推出了 80 nm 半節點(half-node),如同以往,這是由 90 nm 製程透過微影尺寸縮小而來。這類半節點在結構上往往與前一個完整節點非常相似,因此不易辨識,但透過金屬層線距(metal pitch)的詳細比較即可判斷。

如圖所示,結構差異非常有限,僅在 SiOCN 阻障層上有細微調整,且我們觀察到略為增加的閘極長度。

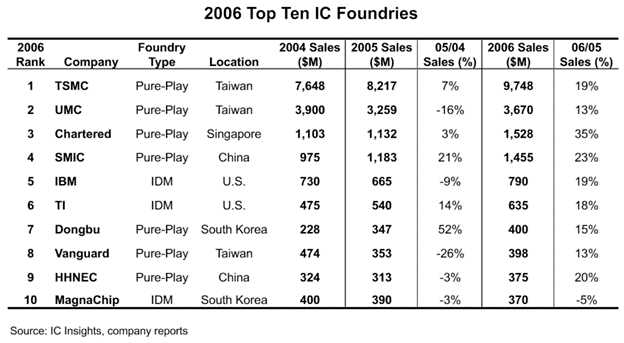

到了 2006 年底,IC Insights 將 TSMC 排名為全球 IC 銷售第四名,同時其晶圓代工規模已是第二名的 2.5 倍以上。

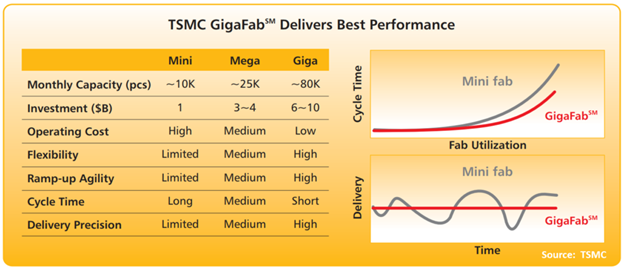

TSMC 也為其兩座 300 mm 晶圓廠創造了「GigaFab」一詞,於 2006 年第四季的總產能為 271,000 片 300 mm 晶圓。在 2006 年的《Business Overview》中指出:「這些『GigaFabsSM』是我們持續精進製造卓越性並不斷實現突破的核心基地。透過接近 100% 的自動化,例如即時晶圓派工、最佳化自動化物料搬運系統(AMHS)路徑的搜尋引擎、產品與非產品晶圓的全自動化處理,以及精實的在製品(WIP)控制,我們的 Gigafab 能夠達成更低的營運成本。」

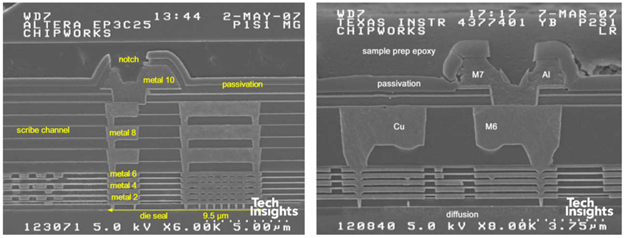

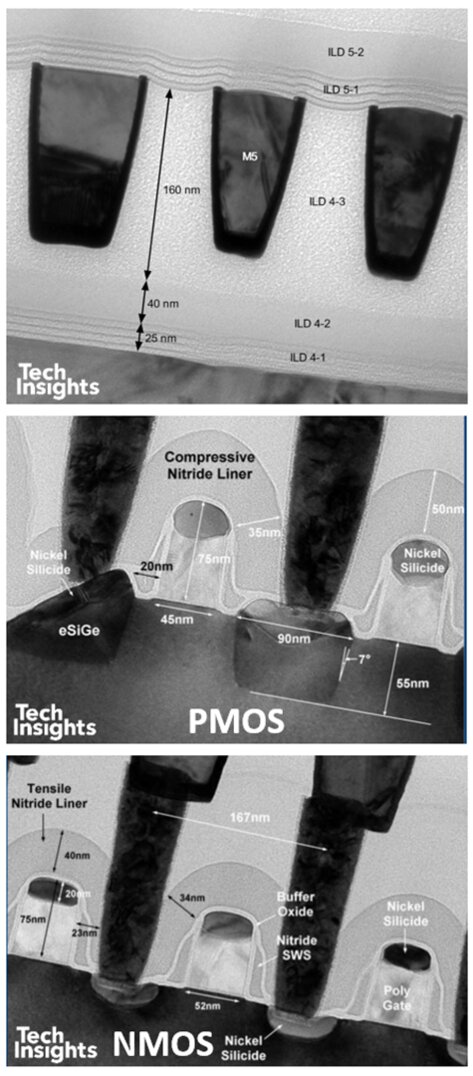

下一個完整節點為 65 nm,在此我們看到一個相當有趣的晶圓代工—客戶客製化案例。除了 Altera 的 FPGA,我們還辨識出一顆由 TSMC 代工的 德州儀器(TI)基頻處理器。雖然後段金屬堆疊相似,但在電晶體結構上則有明顯差異。

TI 的晶片具有明顯較厚的最上層銅金屬(1.6 µm),適合用於電感等 RF 元件;相較之下,FPGA 僅約 0.85 µm。下層金屬線距則較小,以符合 TI 的 65 nm 製程需求。除此之外,下層金屬/介電層堆疊相當類似。該處理器用於 Nokia 手機,而 TI 同時使用自家晶圓廠、UMC 與 TSMC 進行生產,推測其出貨量相當龐大。以下為電晶體結構比較。

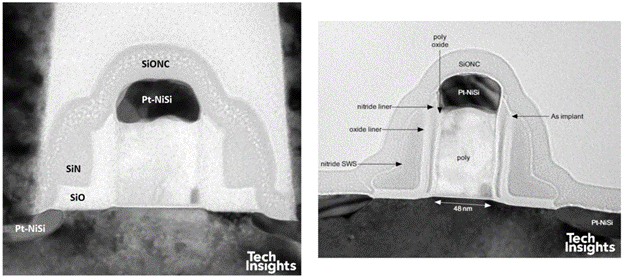

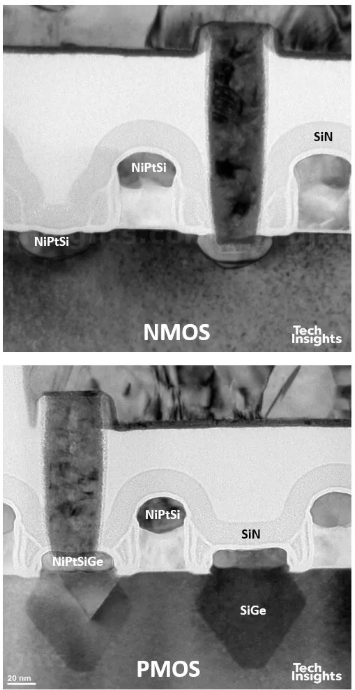

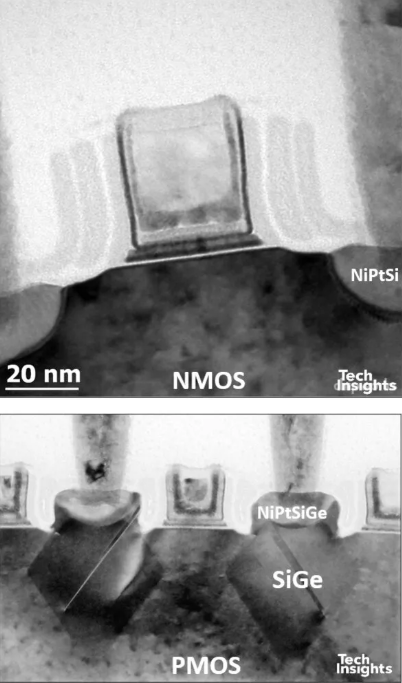

Altera 元件延續 90 nm 與 80 nm 電晶體的趨勢,改用 鉑摻雜鎳矽化物(Pt-doped NiSi),並搭配修改後(可能具應力)的 接觸蝕刻停止層(CESL)。TI 的電晶體則導入其 差動偏移間隔層(DOS)技術與 L 形間隔層——這些結構在 TSMC 的 110 nm 節點已被淘汰。兩者的基板皆旋轉 45°,以形成 <100> 晶向通道。55 nm、約 10% 縮小比例的製程於 2007 年宣布,但我們似乎並未分析當時的實際產品。當然,下一世代製程的研發仍持續進行,傳統(SOI)與高-k 金屬閘極(HKMG)的 45 nm 論文皆於 IEDM 2007 發表。在商業層面,2007 年 Philips 完全出售其持有的 TSMC 股份,這可說是半導體產業中最成功的合資案例之一——Philips 最初約 1,300 萬美元的投資,在 20 年內成長至 超過 100 億美元。同期產能也由約 710 萬片提升至 830 萬片(8 吋等效),其中三分之二來自兩座 300 mm 晶圓廠。當 TSMC 開發其 45 nm 技術時,Intel 已推出 45 nm HKMG 製程,這是電晶體結構上的重大里程碑,以複雜的金屬堆疊取代多晶矽閘極。

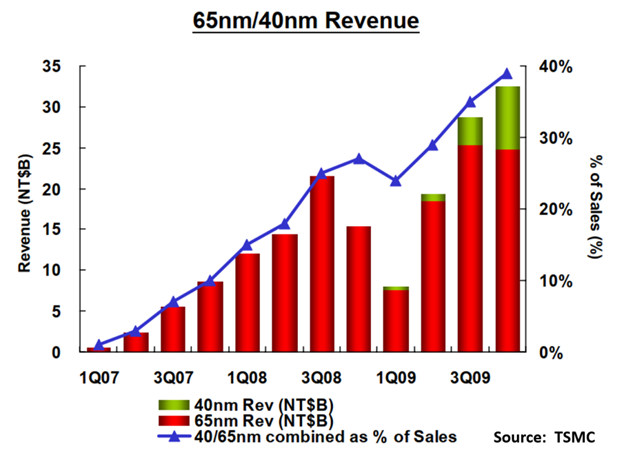

TSMC 在 45 nm 節點採取較為保守的路線,但仍包含重大變革——浸沒式微影、極低介電常數(ELK)材料與應力電晶體。這些變化似乎拖慢了 45 nm 的導入進度,以致該節點實際上被跳過,全面量產轉而集中於規劃中的 40 nm 半節點。根據當時的說法,問題不僅來自新製程步驟的導入,也與製程/版圖互動有關。Mark Liu 在 2009 年第二季法說會中表示:「在這一代,我們發現設計版圖風格非常重要,不同產品的良率差異相當大,而良率偏低的主要原因是設計對版圖的依賴性。所謂的 Design for Manufacturing,用白話說就是,當設計無法完全由設計規則描述時,我們需要額外的演算法軟體來優化版圖,以達到最佳良率。」同時也必須導入並建置新的量測技術(metrology)。2008–2009 年的全球金融危機亦對產業造成衝擊;2009 年全球 IC 市場下滑 10%,但在 2009 年第四季相較第一季出現 47% 的強勁反彈。這一影響在 TSMC 的 65/40 nm 營收曲線中表現得相當明顯。

40 nm 製程承襲了 45 nm 的製程變革,但在公開尺寸上僅有極小的縮減。初期提供 低功耗(LP)、通用(GP)與高效能(GS)三種版本,後來又加入 超低功耗變體。對三種製程的分析顯示,GS 使用 雙應力 CESL 氮化層(DSL:NMOS 拉伸、PMOS 壓縮),並在 PMOS 中導入 嵌入式 SiGe 以增加壓縮應力;GP 亦使用 DSL,但 Ge 含量較低(19% vs. 26%);LP 則延續 DOS 間隔層與 <100> 通道方向,但不使用 DSL 或 e-SiGe。所有版本的下層金屬皆似乎採用 ELK(可能為 Black Diamond II)。

至 2009 年底,TSMC 已擁有 400 多家客戶,全年生產 7,000 多種產品。十年間出貨量由 180 萬片(8 吋等效)成長至 2009 年的 770 萬片,年產能由 190 萬片擴充至 1,000 萬片,反映了 Fab 12 第四期與 Fab 14 第三期的 300 mm 擴建成果。營收亦由約 新台幣 730 億元成長至 約 2,960 億元,十年間成長 超過 400%。

Phase 5 – HKMG 與持續擴張(Expand, Expand, Expand)

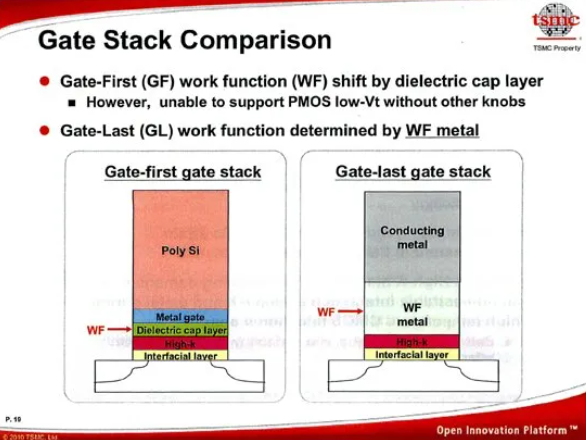

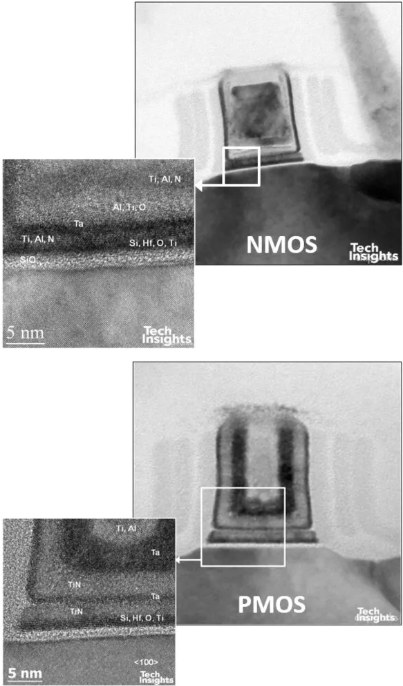

2010 年 7 月,TSMC 宣布於 台中中部科學園區為其第三座 300 mm Gigafab(Fab 15) 動土,規劃分為四個階段。第一期鎖定 40 nm 與 28 nm 製程,後續各期則對應下一代節點。至該年底,Fab 12 擴建至第四期、Fab 14 擴建至第三期,整體產能提升 37%,達到約 每年 250 萬片 300 mm 晶圓。2007 年,Intel 在 45 nm 節點導入 高介電常數金屬閘極(HKMG),採用 gate-last(後置閘極)/置換式金屬閘極(RMG) 技術,並針對 NMOS 與 PMOS 使用不同的功函數材料。IBM 及其合作夥伴則嘗試另一種 gate-first(前置閘極) 技術,透過在 高-k 介電層中使用不同的封帽摻雜來區分 NMOS/PMOS,而在高-k 之上共用金屬與多晶矽。這不只是閘極堆疊的差異——在 gate-last 流程中,所有高溫的源/汲極工程都在高-k 沉積之前完成,並使用假多晶矽閘極;而 gate-first 則會讓高-k 層暴露於高溫的源/汲極製程之中。

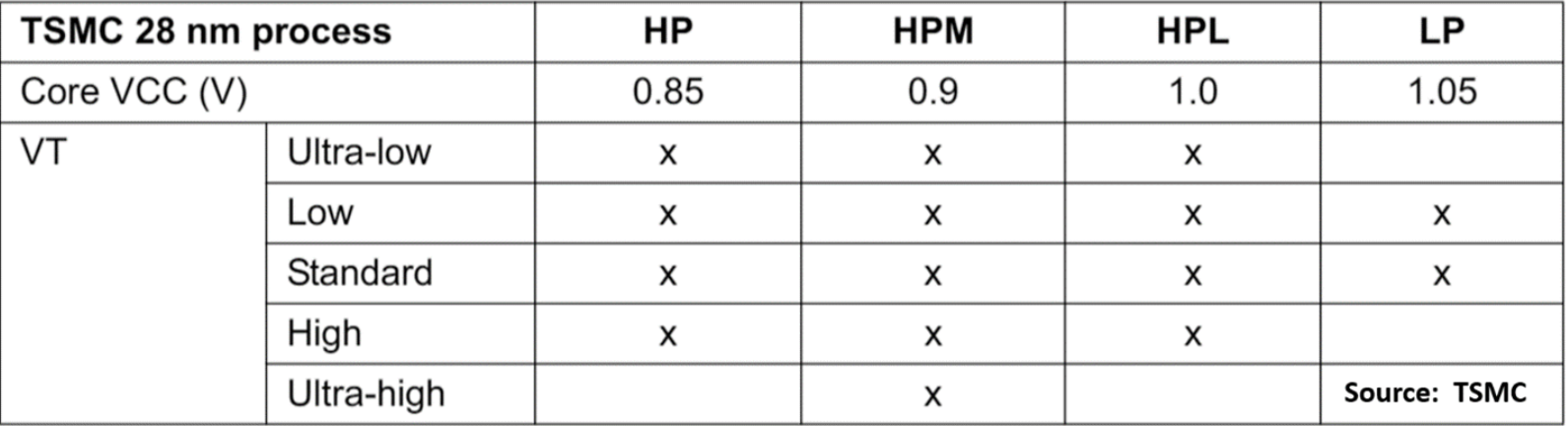

在 32 nm 研發起步後,TSMC 於 28 nm 世代同時進行 gate-first 與 gate-last 的 HKMG 兩條研發路線,並最終選擇 gate-last,此決策於 2010 年 2 月 Executive Forum 對外宣布。同時也揭露將提供三種版本:28HP(高效能,HKMG),28HPL(中速、低漏電,HKMG),28LP(低功耗,採傳統多晶矽閘極),之後又新增 行動應用導向的 28HPM(亦為 HKMG)。

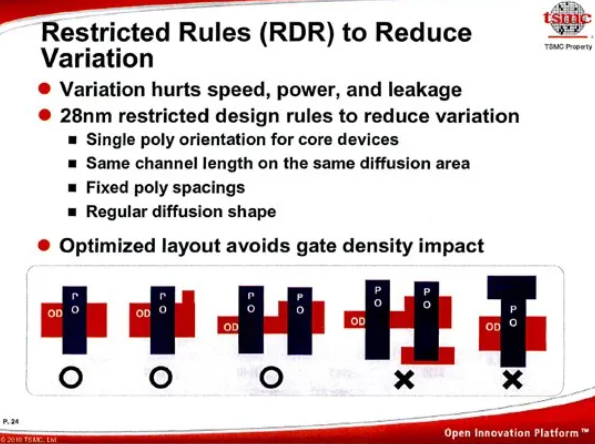

汲取 45 nm 與 40 nm 延遲的經驗,TSMC 導入 受限設計規則(Restricted Design Rules),以降低變異並提升良率。

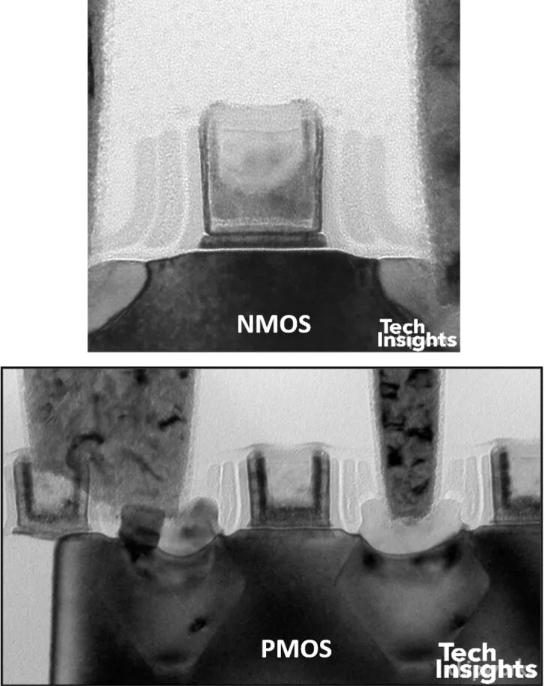

與 40 nm 相同,28LP 持續使用 差動氧化物間隔層(DOS),但這次 PMOS 導入 嵌入式 SiGe(e-SiGe),且不使用雙應力氮化層。

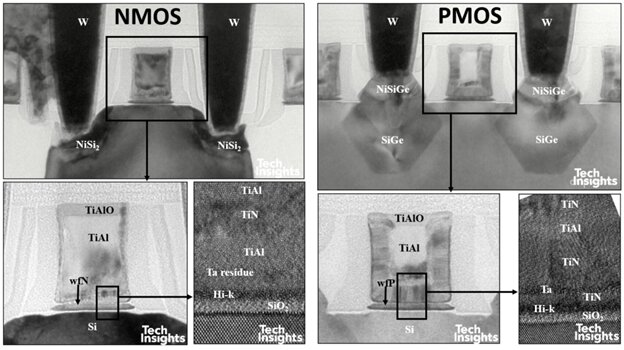

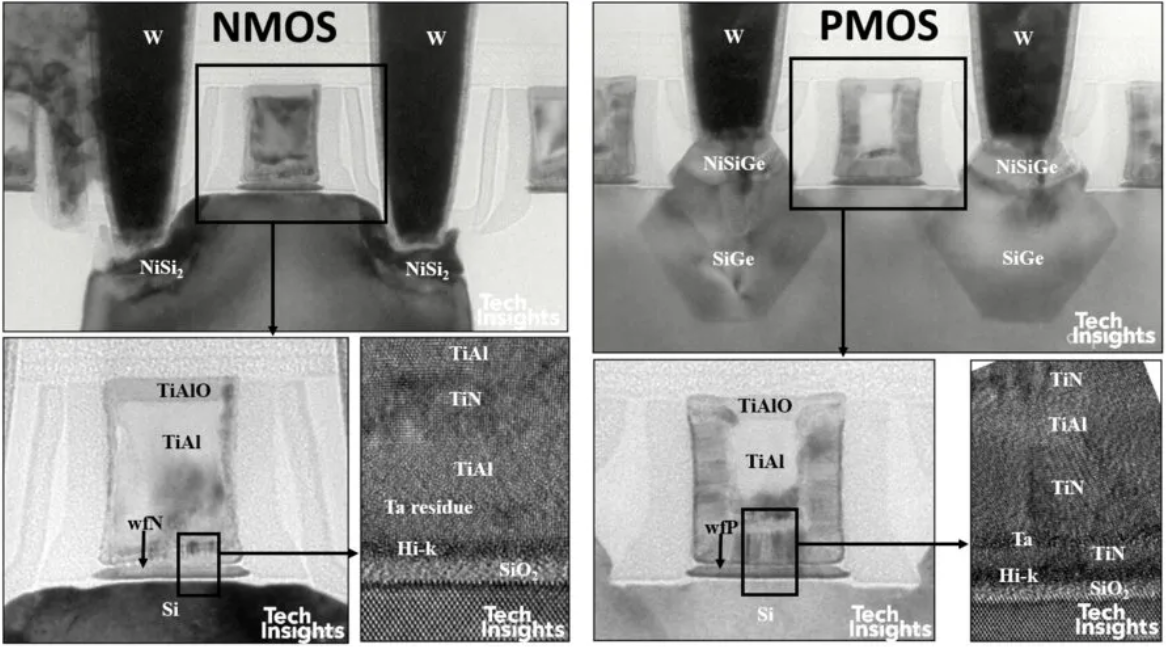

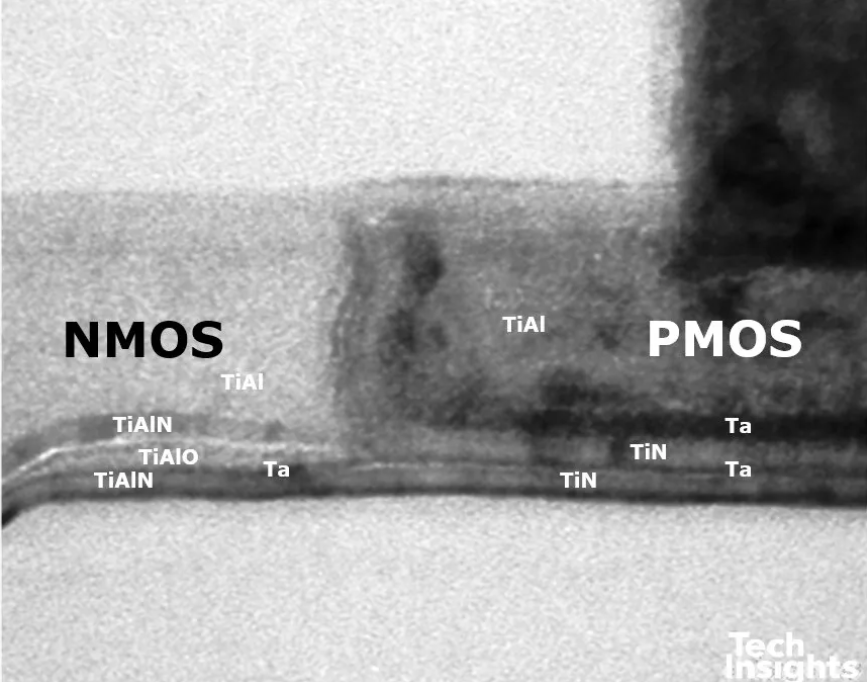

透過將 Ge 含量提升至 40% 並使用 選擇性 (111) 晶面空腔蝕刻,e-SiGe 應變效果進一步強化;推測在 接觸蝕刻停止層中亦存在一定的拉伸應力。通道方向回到 <110>。進入 HKMG 製程後,Xilinx 在其 Kintex-7 FPGA 中採用 28HPL:

高-k 層及其介面氧化層先行形成(high-k first),再沉積假多晶矽閘極;DOS 間隔層演進為 三層 SiN/SiO/SiN。為符合低功耗定位,未在 PMOS 中使用 e-SiGe,但通道方向為 <100>。Altera 則在其 Stratix-V 產品中選擇 28HP。NMOS 外觀相近,但 PMOS 受惠於 e-SiGe,其 Ge 含量提高至約 50%:

作為參考,以下為 Intel 45 nm 電晶體:

兩者的閘極堆疊相似但不完全相同,功函數材料也相近。一個顯著差異在於 金屬置換順序:Intel:先形成 PMOS 金屬,再於 NMOS 區域蝕刻回退並填入 NMOS 金屬;TSMC:順序相反,先 NMOS,後 PMOS

總結而言,28HPM 具有與 28HP 相同的 HKMG 閘極堆疊,但 最小閘極長度更短(32 → 27 nm),且 PMOS 源/汲極的 Ge 含量降至約 30%。28HP 與 28HPM 皆為 <110> 通道方向,對應 (111) 蝕刻的 SiGe 空腔。所有 28 nm 版本的下層金屬似乎皆採用 ELK(可能為 Black Diamond II)。

下表彙整各 28 nm 製程版本。

TSMC 亦於 2010 年 Executive Forum 宣布,下一個節點將是 20 nm 而非 22 nm,以維持 70% 縮小比例,並預計於 2012 年推出。期間,Fab 15 第二期於 2011 年中動工,12 月啟動第三期;第一期設備已完成移入,量產預計於 2012 年初。至 2011 年底,Fab 12 與 Fab 14 的裝置產能已超過 每月 27 萬片,而 Fab 15 完工後預計再增加 超過 10 萬片/月。這是在 2011 年全球半導體市場幾乎零成長的艱困環境下達成的。2011 年 Business Overview 宣布 CoWoS 3D 晶片堆疊的研發成果:「2011 年,我們展示了一個完全可運作的子系統,包含具內建被動元件的邏輯晶片與凸塊,全部在 TSMC 以自有 Chip on Wafer on Substrate(CoWoS™) 技術完成製造與組裝。」CoWoS 是 TSMC 先進封裝發展的重要一環,但其內容足以另文專述。

在研發方面,TSMC 在 28 nm 與 20 nm 節點完成 FinFET 能力驗證與路徑探索後,啟動 14 nm FinFET 的全面研發;同時也投入 450 mm 計畫,並加入位於紐約 Albany 的 G450C(Global 450mm Consortium)——該計畫最終未能延續。2012 與 2013 年,28 nm 產能擴張,使其分別占年終營收的 22% 與 34%。20 nm 於 2014 年初開始量產,快速爬坡後在 第四季貢獻 21% 營收,受惠於旗艦智慧型手機;同年 28 nm 仍占 42% 年營收。20 nm 節點因突破單次曝光解析度極限,關鍵層需採用 雙重圖案化(double patterning),名義 Mx 線距為 64 nm;並引入 **單閘極擴散中斷(single-gate diffusion breaks)**與 M0 在地互連。在電晶體結構上,閘極堆疊轉為 high-k last,即在移除多晶矽後才沉積高-k 介電層。

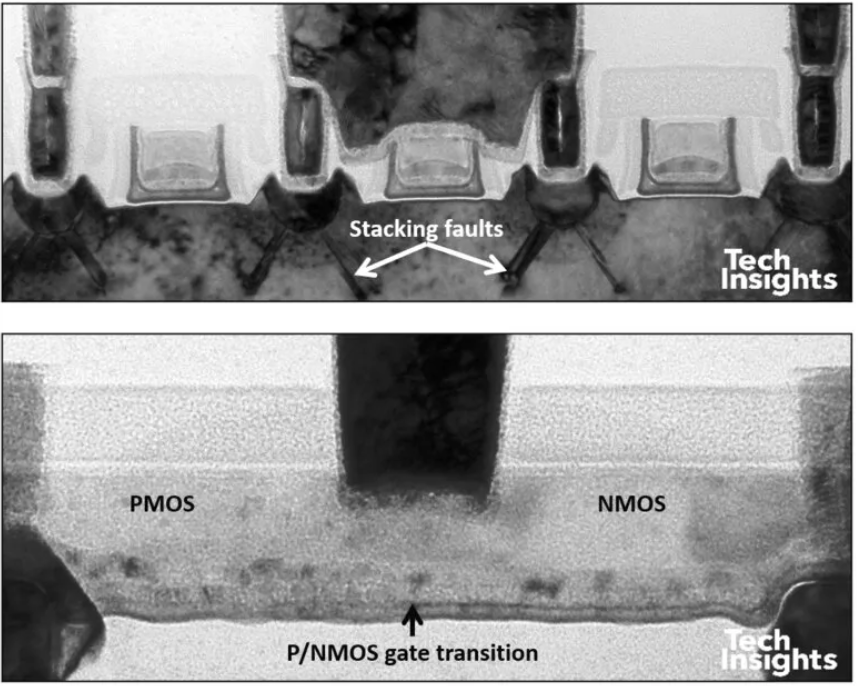

金屬置換順序回到 Intel 式流程(先 PMOS、後 NMOS);同時透過 **堆疊缺陷(stacking faults)**來強化 NMOS 應力。

一般而言,堆疊缺陷並非電晶體中理想的結構,因為若貫穿接面可能造成漏電;但只要侷限於 源/汲極擴散區,通常不會成為問題。直觀來看,此機制是合理的:堆疊缺陷代表晶格中缺失了一層原子;當 閘極長度約 28 nm、通道長度僅剩百個原子間距以內時,若通道兩端各缺少數層原子,便可在通道中誘發 拉伸應力。本篇自 2009 年起算;至 2014 年,TSMC 的晶圓產能由 每年約 440 萬片 12 吋等效增至 約 830 萬片,成長 約 88%,總資本支出約 400 億美元。同期 TSMC 的晶圓代工市占在五年間提升至 54%。前文提及 14 nm FinFET 研發;其後演變為 16 nm FinFET,並於 2015 年第三季投入量產。

Phase 6 – FinFETs!

To be continued