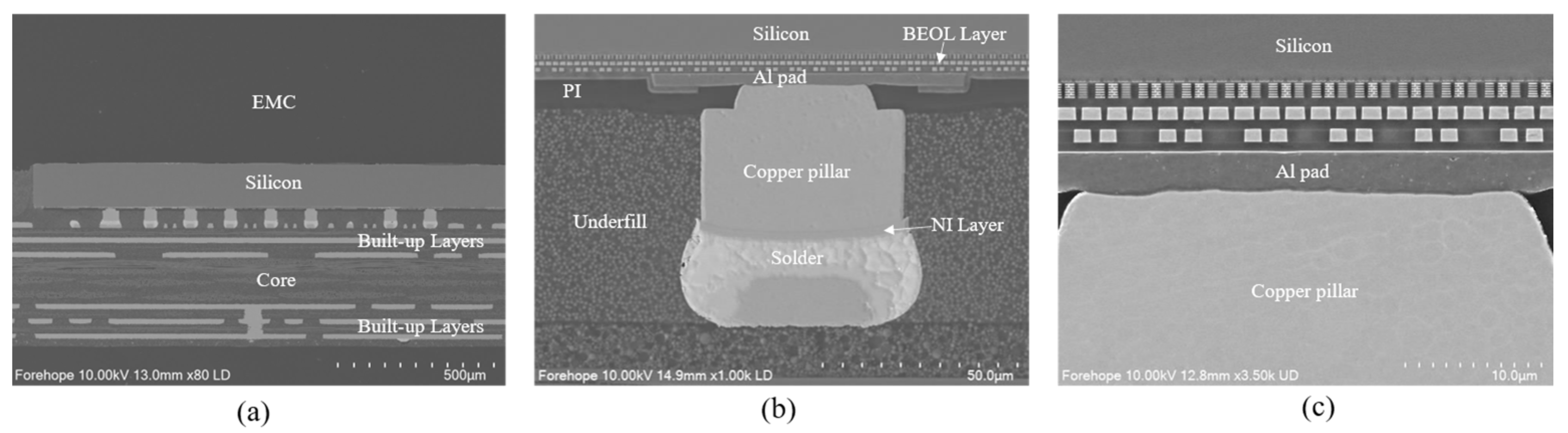

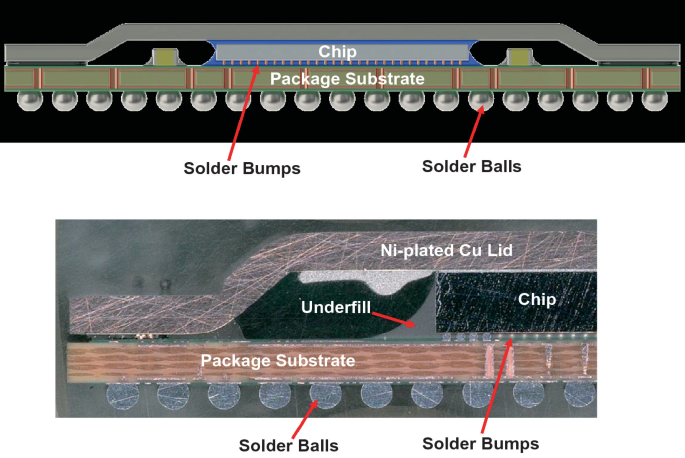

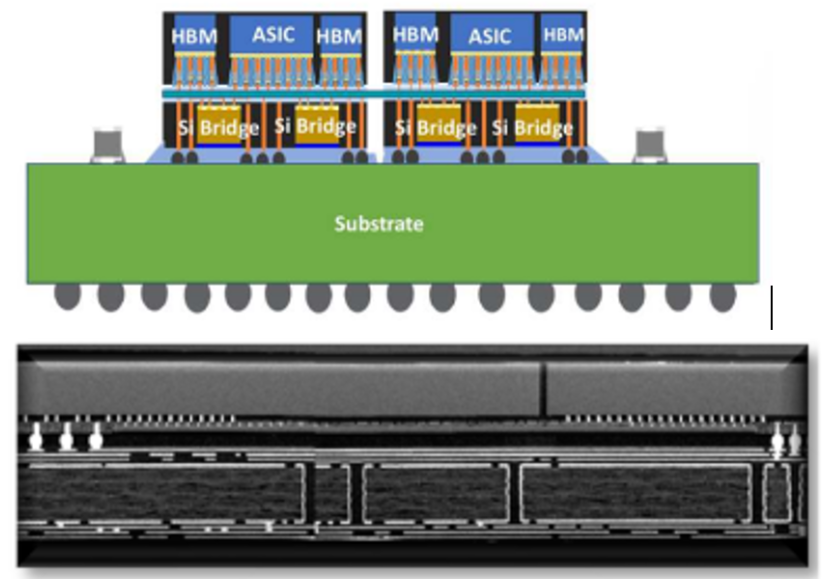

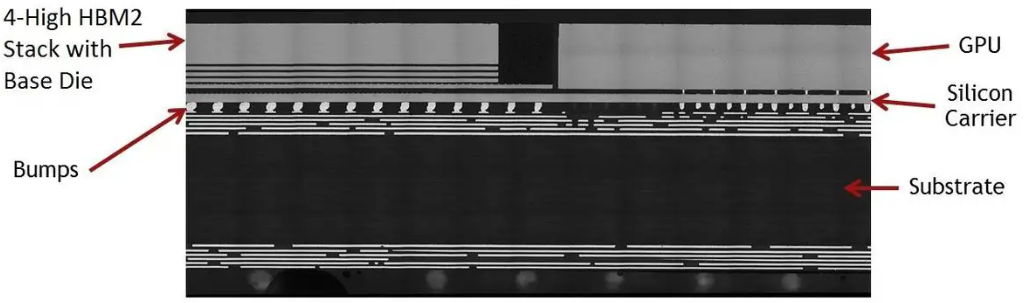

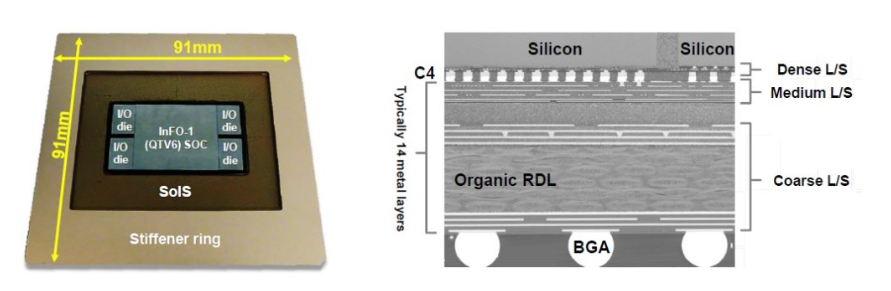

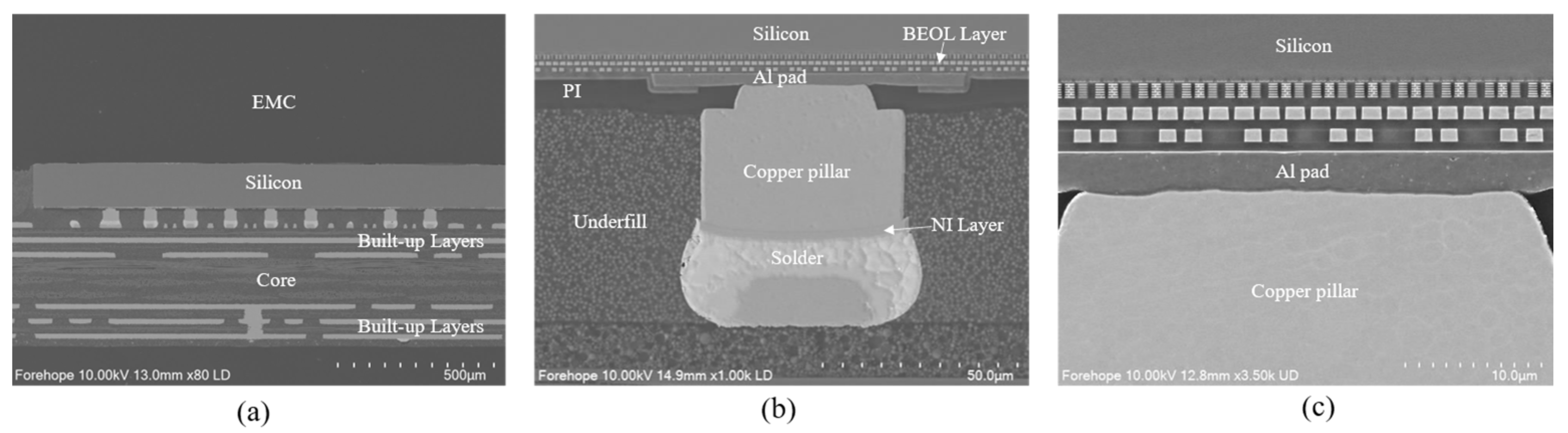

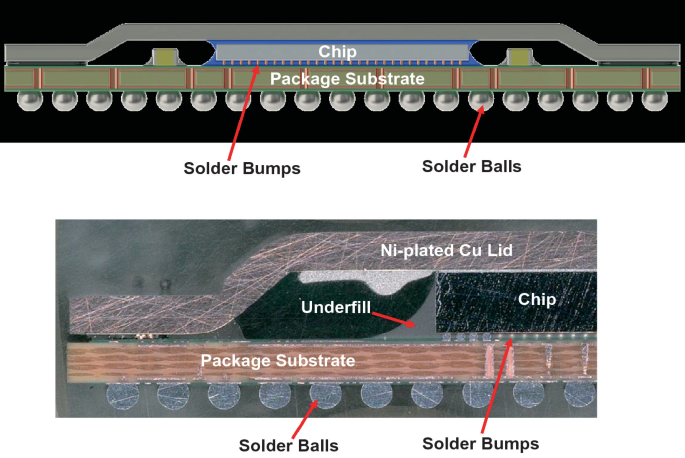

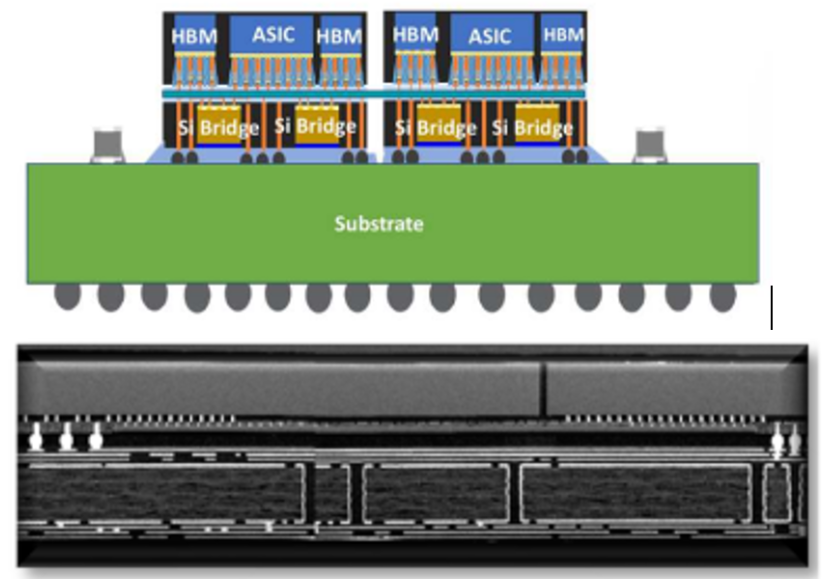

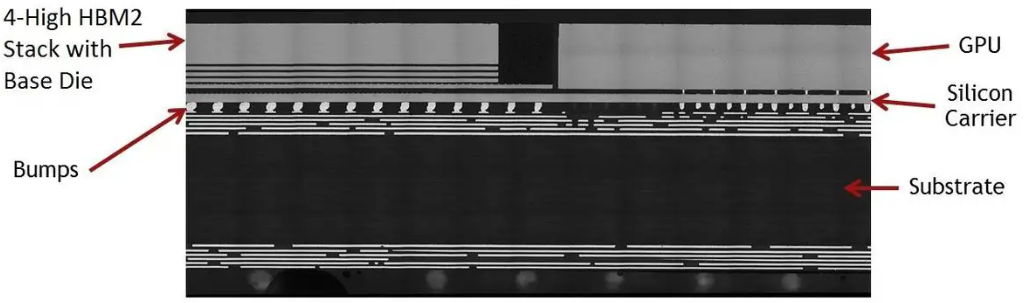

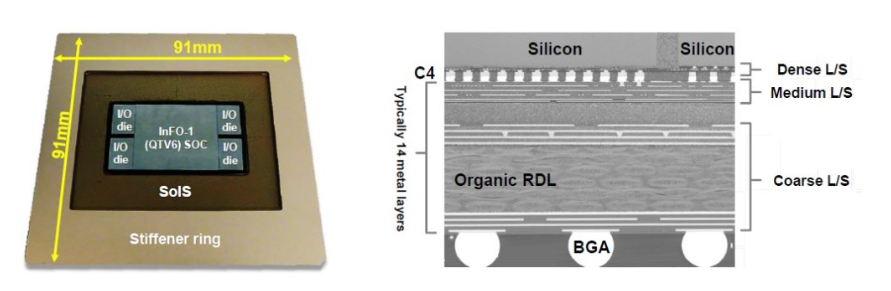

晶片封裝的主要職責是完成各晶片之間的電氣連接,如果說BEOL是on-chip interconnect的話,那麼封裝就是off-chip interconnect。隨著晶片製程技術的進步,晶片內部的線路越來越細密,單位面積內的I/O數量也大幅增加,這對封裝技術提出了更高的要求。我們通過截面分析,可以深入了解不同封裝技術的結構特點及其對性能的影響。以下是各種封裝技術的截面結構分析示例。

晶片封裝的主要職責是完成各晶片之間的電氣連接,如果說BEOL是on-chip interconnect的話,那麼封裝就是off-chip interconnect。隨著晶片製程技術的進步,晶片內部的線路越來越細密,單位面積內的I/O數量也大幅增加,這對封裝技術提出了更高的要求。我們通過截面分析,可以深入了解不同封裝技術的結構特點及其對性能的影響。以下是各種封裝技術的截面結構分析示例。